ESD対策新時代(2/4 ページ)

HBM/MMへの対応

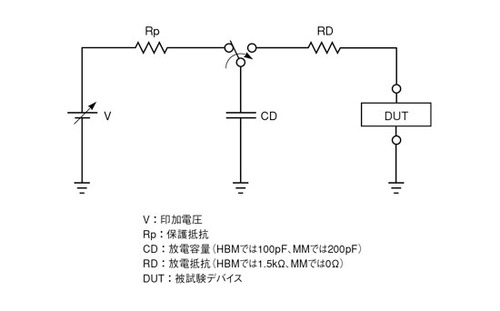

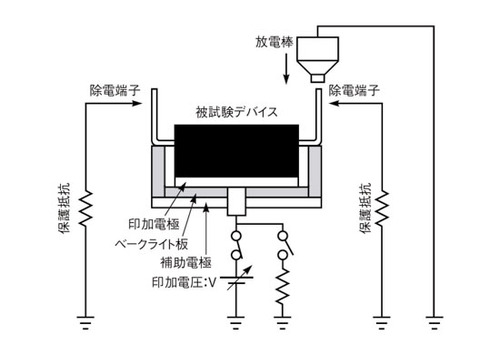

ここでは、HBM/MMにおけるシミュレーション試験法と保護回路について説明する。図3に示したのは、HBM/ MMシミュレーション試験法の等価回路図である。これを用いたシミュレーション試験法は、簡単にいえば次のようなものになる。

まず、導体である人体などの外部静電気帯電物体に対し、放電容量CDに試験電圧Vを印加することによって電荷を蓄積する。その上で、適切な放電抵抗RDを介して被試験デバイスDUTへ電荷を放出する。これにより、実際のHBMやMMを再現しようというものである。

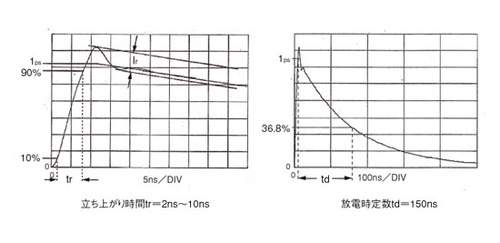

図4に示したのは、IEC(International Electrotechnical Commission)/JEITA(Japan Electronics and Information Technology Industries Association)/ JEDEC(Joint Electron Device Engineering Council)*5)*6)*7)で、HBMの試験方法として規定されている短絡負荷での放電電流の波形である。放電電流の立ち上がり時間trは、2ns〜10nsとかなり遅い。これは、放電容量CDに蓄えられた電荷を短絡状態で放電する場合でも、放電経路に形成されるL(インダクタンス)成分が放電電流の立ち上がりを抑えるように作用するためだ。この放電により、デバイス内部の寄生ダイオードや保護トランジスタがブレークダウンし、HBMサージによる電荷が流れてゆく。

一方、放電時定数tdは150nsと大きい。そのため、HBMサージが印加されたデバイスでは、ゲート酸化膜の破壊などの電界的破壊ではなく、保護トランジスタやダイオードなどのPN接合部の破壊、あるいはポリシリコン保護抵抗の破壊といった熱的破壊を起こすのが一般的である。熱的破壊は、平均破壊電力と放電時定数との関係から、断熱破壊、熱拡散型破壊、熱平衡破壊などに分類される。従来のESD保護回路の設計手法では、各素子におけるこれらの関係を用いて最適な保護設計を行うのが一般的であった。

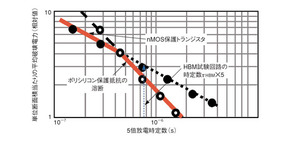

図5はポリシリコン保護抵抗とnMOS保護トランジスタそれぞれの平均破壊電力Paveと5倍放電時定数である5τとの関係を表している。ポリシリコン保護抵抗の破壊は(Pave)X(τ)=一定の断熱破壊となり、nMOS保護トランジスタの破壊は(Pave)=K(τ)−0.5の熱拡散型破壊となる。

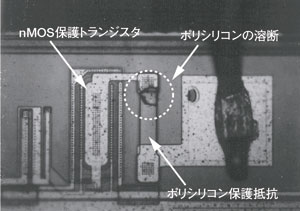

図5から、これら2つの保護素子を入力端子に直列接続した保護回路の場合、破壊部位が試験回路の時定数に対応して変化することが分かる(各保護素子が試験回路の時定数に影響しないことが前提)。また、「ポリシリコン保護抵抗+nMOS保護トランジスタ」という保護回路は、HBM試験条件においてポリシリコン保護抵抗の破壊という結果になると予測される。写真1は、図5に対応した各素子を利用した製品のHBM試験による破壊個所を示している。この写真から、実際にポリシリコン保護抵抗が溶断破壊していることが確認できる。

図5から、この例の場合、HBMサージに対する耐性は、ポリシリコン保護抵抗の幅を50%程度太くすることで、平均破壊電力がnMOS保護トランジスタと同等程度まで向上(相対値が2から3に向上)することが予想される。その結果、保護回路のHBMサージ耐性が向上する。

CDM/CPMへの対応

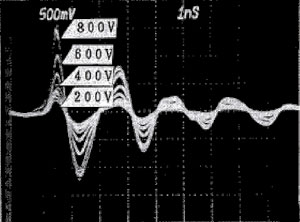

続いて、CDM/CPMのシミュレーション試験法と保護回路について説明する。図6に、CDMの1つであるCPMのシミュレーション試験法*8)の具体的な実施方法を示した。写真2は、試験における放電電流の波形である。HBMシミュレーション試験法に対し、CPMシミュレーション試験法の放電電流は、非常に立ち上がりが速く(trが0.2ns未満)、放電時間が非常に短い。半導体デバイスにこの種のサージが印加されると、保護回路がブレークダウン動作によって電荷を流す前に、内部回路に過渡電圧が印加され、ゲート酸化膜の破壊といった電界的破壊現象が起きてしまうことが多い。

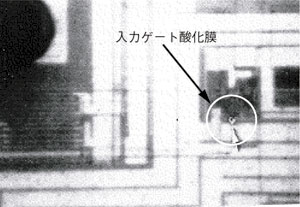

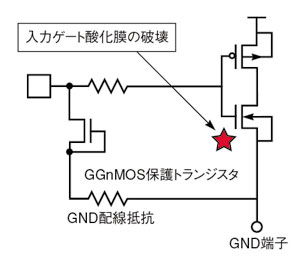

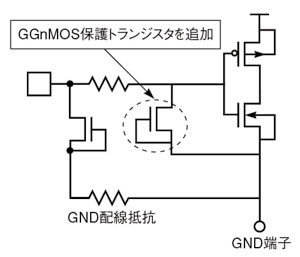

図7は、いわゆるGGnMOS(gate grounded nMOS)を保護トランジスタとして用いた入力保護回路の例である。この入力端子のCDM耐性は500V未満と低いことが確認された。写真3に示したのは、CDM試験による破壊個所の解析結果である。破壊原因は、保護トランジスタのグラウンド(GND)ラインと入力ゲートのGNDラインが分離され、保護トランジスタとGND端子の間の配線抵抗が大きくなっていることだ。写真2のような立ち上がりの速いサージが端子に印加されることで、図7の保護トランジスタからGND端子に電流が流れる間、入力ゲートに過渡電圧が印加されるため破壊に至るのである。この例の場合、図8のように入力トランジスタのゲートとGNDの間に直接、GGnMOS保護トランジスタを挿入することが対策の1つとなる。その結果、CDM耐性は2kV以上に改善された。

CDMのシミュレーション試験法(FICDM/CPMを含む)は、JEITA/ JEDEC/ESDA(Electrostatic Discharge Association)などで規格化されているが、それぞれピーク電流値などが異なっている。そのため、IECの専門委員会(Technical Committee)であるTC 47(半導体デバイス)/TC101(静電気)によって構成されるJWG(Joint Working Group)において、国際的な標準化を行うための活動が進められている。

脚注

※5…福田保裕, "IEC61340-3-1 Ed2.0概要解説", EMC誌, 2006-8月号-No220, pp.99〜101

※6…EIAJ ED-4701/300

※7…JEDEC STANDARD JESD22-A114-B

※8…Y.Fukuda atc, " ESD Protection Method Evaluation by HBM and CDM (Charged Package Method)", 1986 EOS/ESD Symp. Proc., pp.193〜199

Copyright © ITmedia, Inc. All Rights Reserved.

図3 HBM/MMシミュレーション試験法の等価回路図

図3 HBM/MMシミュレーション試験法の等価回路図  図4 HBMシミュレーション試験法による放電電流波形

図4 HBMシミュレーション試験法による放電電流波形  図5 保護素子の平均破壊電力と試験回路の時定数との関係

図5 保護素子の平均破壊電力と試験回路の時定数との関係  写真1 保護回路の破壊個所

写真1 保護回路の破壊個所  図6 CPMシミュレーション試験法

図6 CPMシミュレーション試験法  写真2 CPMシミュレーション試験法の放電電流

写真2 CPMシミュレーション試験法の放電電流  写真3 CDM試験による破壊個所

写真3 CDM試験による破壊個所  図7 CDM耐性の低い入力保護回路

図7 CDM耐性の低い入力保護回路  図8 CDM耐性の改善策

図8 CDM耐性の改善策