オペアンプ設計の要諦をつかむ(5/5 ページ)

出力段の構成方法

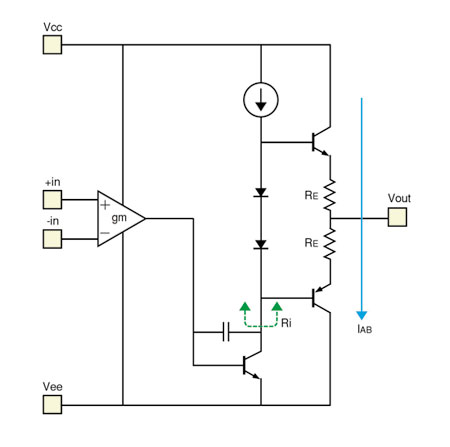

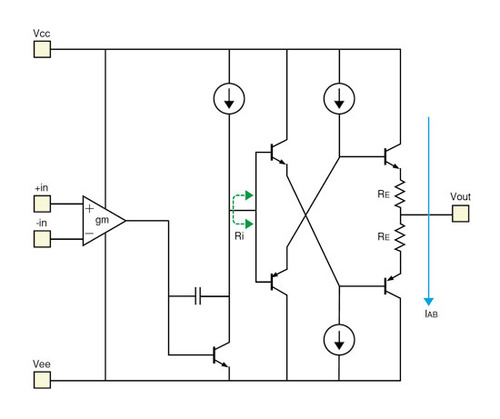

ここまで差動入力段とゲイン段について述べてきたが、最後に出力段にも簡単に触れておきたい(図7、図8)。

図7、図8に示すのは、いずれもよく使われているAB級出力バッファ回路である。出力段の貫通電流IABが同じであるなら開ループでの出力インピーダンスRoはほぼ等しく、以下のようになる(re=1/gmとする)。

その値は、例えばIABが1mAでREが10Ωだとすれば以下に示す値になる。

この値は小さいほど優れており、出力インピーダンスがゼロに近いほど容量性負荷に強いといえる。なぜなら、Roと容量負荷による位相遅れが少ないからである。

図7、図8の2つの回路で最も異なる点は、ゲイン段と負荷側(出力段)のアイソレーションにある。図7では、ゲイン段から見た出力段の入力インピーダンスRiは、負荷がRL、トランジスタの電流増幅率をβとすると以下の式で表すことができる。

一方、図8では以下のようになり、図7の場合よりもはるかに大きい。

これは、図8の回路であれば、ゲイン段が負荷の影響を受けにくいと言い換えることもできる。それにより、ゲイン段の設計が容易になる。さらにゲイン段のゲインを大きくできるという利点もあり、リニアリティを保つのにも有利である。

基本を押さえる

ここまで、オペアンプの安定性やノイズといった特性に関して、あるいは差動入力段、ゲイン段、出力段の構成などについて解説を進めてきた。しかし、本稿で取り上げた事柄はその一部に過ぎず、実際にはもっと議論の余地がある。ましてや、実際の設計に当たっては、ほかのパラメータについても同時に考慮しなければならず、本稿の内容だけではまったく十分とはいえない。とはいえ、最も基本的かつ重要な部分については押さえることができたと考える。もちろん、本稿で説明したことを踏まえなくともオペアンプを使うことはできる。しかし、本稿で取り上げた事柄には、オペアンプを設計する際はもちろん、使用時においても、改良を加えたり、問題に対処したりする際に理解しておくべきことがたくさん含まれている。

オペアンプは、基本回路ブロックとしてIP化されていたり、既存の回路を再利用したりする形で利用することが多い。そのため、オペアンプそのものをじっくりと設計する機会は少ないかもしれない。しかし、アナログ回路設計においてオペアンプが基本であることは、今も昔もこれからも変わらない。オペアンプの内部についても、ある程度理解しておくことは必要であろう。

Copyright © ITmedia, Inc. All Rights Reserved.

図7 AB級出力段の例(その1)

図7 AB級出力段の例(その1) 図8 AB級出力段の例(その2)

図8 AB級出力段の例(その2)