オペアンプ選びの道しるべ:「正解」を導き出すためのポイントをつかむ(2/3 ページ)

データシートの読み解き方

オペアンプを選択する際には、その全体像を理解する必要がある。その方法の1つは、データシートの構造を把握することだ。

データシートの最初のページは、その製品の主要な機能と、対象とする用途を理解する上で重要な部分である。「速い」に代表される宣伝目的の単語は差し引いて、まずは実際の速度に関する数値を探し出す。そうすれば、その製品が自分の用途に適しているか否かがすぐにわかる。最初のページには、その製品の製造プロセスについて記載されていることもある(別掲記事『製造プロセスによる特徴』を参照)。

・絶対最大定格

通常、データシートの2ページ目には、絶対最大定格が記載されている。この項には、部品を使用可能な電圧と温度の最大値が必ず示してある。この目立つ位置に存在することから、絶対最大定格が選択において重要であることは明らかだ。

この値は、絶対的な限界値である。つまり、使用時にはそれらの限界値をほんのわずかでも超えてはならない。

・表

データシートには、動作電圧、DC性能、AC性能などに関する表も掲載されている。各表には、各値が何ボルトの電圧で動作させた場合のものであるかが明記されている。

ここで1つ注意すべき点がある。例えば、データシートの最初のページに、その製品は最小2.7Vで動作すると記載されているとしよう。しかしながら、各表には動作電圧の条件が3Vだと記載されている場合がある。つまり、確かに2.7Vでも動作するのかもしれないが、データシートで3Vを条件としている項目については、表に書かれた値が実現されるとは限らないということだ。従って、より低い電圧における特性評価をメーカーに依頼するか、自分で評価する必要がある。表に示された値は、あくまでもメーカーが満たさなければならない契約上の要件である。言い換えれば、メーカーはすべての動作電圧で各項目の値を保証しているわけではない。

・グラフ

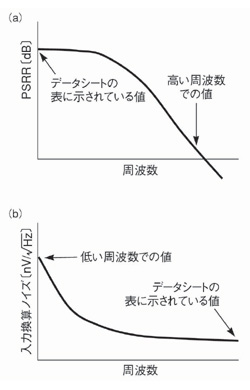

データシートでは、表のページの次にグラフのページが続く。これらのグラフは正式な仕様を表しているわけではないのだが、非常に重要な情報である。例えば、表に示されているPSRR(power supply rejection ratio:電源電圧変動除去比)の値は高いのに、グラフを見ると周波数の増加に伴って値が著しく減少するという事実が示されている場合がある(図3(a))。自分にとって、1MHzにおけるPSRRが重要なのであれば、グラフを参照してその条件でのPSRRの値を調べなければならない。また、そのグラフは、自分が使用する電源電圧条件とは異なる電圧における結果であるかもしれない。

同様に、表に示されている電圧ノイズの値は、一般に高い周波数におけるものである。そのオペアンプをDCまたは低い周波数の用途で利用するのなら、グラフを参照してその条件でのノイズの値を調べる必要がある(図3(b))。

メーカーによっては、実際にはあまり高くはない仕様がより良く見えるようなグラフを掲載している場合もある。すべてのグラフを参照し、それらの結果から何がわかるか考えてみるとよい。例えば、10pFの出力容量によって90%のオーバーシュートが生じることがグラフに示されているとしたら、その製品は安定性に欠ける可能性が高い。

・概説/用途

一般的なデータシートでは、グラフの次に概説や用途について記した項がある。ここでは、その製品の特性や、適切な用途、特殊な機能について知ることができる。なお、用途の項には、「出力を高くしすぎると部品が焼損する」といった警告などが記載されていることもある。

(発注用の)部品番号や末尾番号(suffix)は、データシートの後ろのほうに掲載されていることが多い。ただし、TI社のように表紙にこの情報を掲載するメーカーもある。パッケージオプションなどが存在する場合には、それぞれに固有の部品番号が付与されている。メーカーによっては、RoHS(restriction of hazardous substances)指令対応の鉛フリー製品にそのことを明示するための番号を記載している場合もある。部品番号は、例えば4000個リールなどのように、出荷形態によっても異なる。不適切な部品番号を用いて発注したために、意図していたのとは異なるパッケージの製品が届いてしまうと、その製品または設計済みの基板のどちらかが無駄になってしまう。このような誤りを犯すと、開発期間に数週間〜数カ月のロスが生じることになりかねないのでくれぐれも注意が必要である。

データシートの最後には、パッケージの外形図やプリント配線板への配置例が掲載されていることが多い。設計によっては、パッケージの高さが、満たすべき重要な仕様であることもある。

製造プロセスによる特徴

オペアンプの選択は仕様ベースで行うべきであり、それを製造したプロセスについては気にする必要はないと考えるメーカーもある。その主張にも一理あるが、多くの場合、設計者は仕様とともに半導体プロセスについても考慮すべきである。そうすることによって、部品を大まかに分類し、仕様についてある程度の仮定を行うことができるからだ。

メーカーがもともとオペアンプの製造に使用していたのは、FETやMOSFET(metal oxide semiconductor FET:金属‐酸化物‐半導体電界効果トランジスタ)ではなく、バイポーラトランジスタであった。バイポーラプロセスで製造した製品は高電圧での動作が可能であり、一般的には高速になる。また、バイポーラトランジスタはトランスコンダクタンスが高いため、設計が容易である。

通常よりもアイソレーション(分離構造)に優れたプロセスを用いれば、内部の浮遊容量が通常のプロセスの1/10程度にもなるため、回路はかなり高い周波数で動作可能になる。この種のプロセスでは誘電体分離(dielectric isolation)が用いられていることが多い。この場合、各トランジスタがそれぞれガラスで分離されたくぼみの中にあるような構造となる。また、トレンチ分離のみを用いるプロセスもある。この場合、トランジスタの側面はガラスで分離されているが、底面は従来のバイポーラプロセスのように接合分離となっている。トレンチ分離を用いた部品の速度は通常のバイポーラよりは高速だが、完全な誘電体分離が用いられているものほどには速くない。誘電体分離では、基板に寄生サイリスタ(SCR:silicon controlled rectifier)が形成されることがないため、ラッチアップも発生しない。

誘電体分離の欠点の1つは製造コストが高くなることである。それ以外にも、すべてのトランジスタをガラスの隔壁で囲むという構造は、接合分離構造に比べて熱伝導性が10倍も低いという欠点がある。そのため、大電流出力が求められるオペアンプに誘電体分離が用いられることはまれである。

オペアンプの代表的な製造プロセスとしては、もう1つCMOS(complementary MOS:相補型MOS)が挙げられる。CMOS製品は、製造プロセスにおける工程数が少ないため、そのコストは安い。またCMOS製品は、一般的に動作電流が少ない。

CMOSの最大の特徴の1つは、入力バイアス電流が非常に少ないことだ。例えば、TI社のCMOSオペアンプ「OPA2355」の入力バイアス電流は0.05nAである。この値は、JFET(junction FET)入力の製品に次いで少ない。

12V系のCMOSプロセスも存在するが、CMOS製品は通常5V以下で動作する。初期のCMOS製品は、CMOSの動作電流が少ないという特徴を生かしていたため、電圧ノイズが大きいという問題があった。ただし、電圧ノイズが大きいというのはCMOSの本質的な性質ではなく、入力部分でバイアス電流を少なくし、小型のトランジスタを使用するという設計上の決断によるものである。例えば、National Semiconductor社のCMOSオペアンプ「LMV751」は、大きな入力トランジスタを使用し、電流値を高めに設計しているため電圧ノイズは少ない。

もう1つ、オペアンプの製造プロセスとしては、BiCMOS(bipolar‐CMOS)プロセスがある。このプロセスでは、1つのチップ上にバイポーラとCMOSの両方のトランジスタを形成することができる。

使用例はあまり多くはないが、JFETに対応したバイポーラプロセスも有用である。これはバイポーラプロセスに、JFETを形成するためのマスク処理を追加したものだと言える。JFETは、CMOSトランジスタと同様に入力バイアス電流が少ない。National Semiconductor社の「LF411」やAnalog Devices社の「AD549」など旧式のJFET製品は、CMOSが普及する前にバイアス電流の少ない製品として提供されていた。最近では、バイアス電流は少ないが高速な、いわば現代的なJFET製品も提供されている。例えば、TI社の「OPA656」の帯域幅は500MHzである。またJFETは、ウェーハ基板内の拡散層の中に埋まっているような構造であるため、入力換算ノイズがCMOSトランジスタよりも小さい。CMOSトランジスタはチップの表面にあるため、ノイズの原因となる格子欠陥や不純物の影響を受けやすいからだ。

CMOSとJFETの製造手法にはトレードオフが存在する。CMOSの特性はリソグラフィ処理で決まるが、JFETの特性は拡散処理に依存する。従って、CMOS製品のほうが、差動入力ペアトランジスタの整合性が高く、オフセット電圧が小さく、ドリフトが少ない。

バイポーラよりも高速であることが要求される用途では、シリコンゲルマニウム(SiGe)プロセスが使用される。SiGeプロセスは、ベース領域での電子の移動度が高く、ベース領域を薄くでき、エミッタ電流密度が高いことから、帯域幅が1GHzを超えるオペアンプを製造可能である。その半面、SiGeプロセス製品は、消費電流が多く、ほかのすべての高速部品と同様に安定性の面で問題がある。SiGeプロセスは、高速A-Dコンバータ用の差動入力アンプや高速通信アンプなどで使用されている。

そのほかにはガリウム砒素(GaAs)プロセスがある。GaAsプロセスは、SiGeプロセスよりも電子移動度が高くてベース領域が薄く、非常に高速である。シリコンプロセスと同様の処理工程により、10GHz以上で動作する製品を製造できる。GaAsプロセスの欠点としては、シリコンとは異なり酸化絶縁膜の形成が容易ではないことが挙げられる。シリコンプロセスのシリコン酸化膜はガラス製で、異なる金属層を分離することができる。一方、GaAsプロセスにはこの性質がなく、動作電流もシリコンプロセスより高い上に、コストもかかる。

さらに、SOS(silicon on sapphire:シリコンオンサファイア)という特殊なプロセスもある。このプロセスでは誘電体分離が用いられ、誘電体分離を用いたシリコン酸化物プロセスと同程度に高速なトランジスタを実現できる。また、トランジスタの分離がガラスではなくサファイアで行われるため、熱伝導性は誘電体分離を用いたシリコンプロセスほど低くない。このためSOS製品は高速で、出力電力も大きくとれるという特徴を備える。バイポーラプロセスよりもマスク工程の少ないCMOSプロセスのフローでSOS製品を製造することも可能である。

Copyright © ITmedia, Inc. All Rights Reserved.

図3 データシートに記載されるグラフの例 データシートの表は、性能が高く見えるように書かれていることがある。例えば、データシートの表にDCにおけるPSRRが示されていることがあるが、この条件でPSRRが問題になるケースは必ずしも多くない。一方、データシートのグラフには、PSRRの周波数特性が示されている。それを見ると、高い周波数においてPSRRが急激に低下していることがある(a)。同様に、データシートの表には、高い周波数における入力換算ノイズが示されていることがあるが、この領域でのノイズは小さい(b)。

図3 データシートに記載されるグラフの例 データシートの表は、性能が高く見えるように書かれていることがある。例えば、データシートの表にDCにおけるPSRRが示されていることがあるが、この条件でPSRRが問題になるケースは必ずしも多くない。一方、データシートのグラフには、PSRRの周波数特性が示されている。それを見ると、高い周波数においてPSRRが急激に低下していることがある(a)。同様に、データシートの表には、高い周波数における入力換算ノイズが示されていることがあるが、この領域でのノイズは小さい(b)。