外付け抵抗が不要な2入力加算SH回路:Design Ideas

本誌2008年3月号の本コーナーで、筆者は外付け抵抗を使わずに2倍増幅を実現するサンプルホールド回路(以下、SH回路)を紹介した*1)。今回は、外付け抵抗を使わないで2入力加算機能を実現するSH回路を紹介する。

アナログ電圧の加算値をサンプリングする場合、最も一般的に用いられるのは、アナログ加算回路の後段にSH回路を接続する方法である。典型的なアナログ加算回路は、オペアンプを反転増幅構成とし、加算したいアナログ電圧の数に応じて入力部を並列に設ける形になる。この構成では、1個のオペアンプと高精度の抵抗が少なくとも3個(2入力の場合)必要となる。これらの抵抗の値は、加算回路の帯域が狭くなることを避けたいなら、極力小さくするのが望ましい。ところが、この回路構成で抵抗値を小さくすると、抵抗で消費される電力が増大してしまう。

また、こうした加算回路を使用するSH回路にはもう1つの欠点がある。その欠点は、2つの入力電圧の値が近く、逆の極性を持つ場合に顕在化する。その場合、入力電圧の大きさによらず、2入力の絶対値が同等ならば、加算値はほぼ0になる。こうした小さな電圧を扱う場合、その電圧(電荷)を蓄積するコンデンサに寄生容量から流入する電荷による誤差が相対的に大きくなってしまうのだ。

アナログ電圧の加算値をサンプリングする別の方法として、入力チャンネルごとにSH回路を用意し、その後段に上述した加算回路を配置する構成が考えられる。これであれば寄生容量による誤差の問題は起きないが、加算回路で使用する抵抗での電力消費の問題は残る。

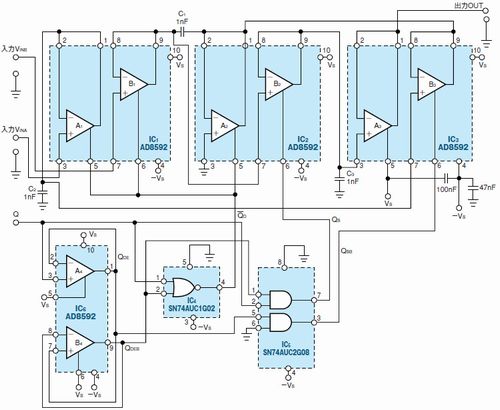

本稿では上記2つの問題点を解決する2入力の回路を紹介する(図1)。この例では、2008年3月号で紹介した2倍増幅SH回路と同様に、ボルテージフォロワ構成の各オペアンプ(以下、フォロワアンプ)として「AD8592」(米Analog Devices社製)を使用した*2)。

図1 2入力加算機能付きのSH回路 この回路では、2つの入力VINAとVINBがコンデンサC1とC2によって同時にトラッキングされる。これらのコンデンサに保持された電圧がサンプリング周期内で加算され、コンデンサC3に保持される。

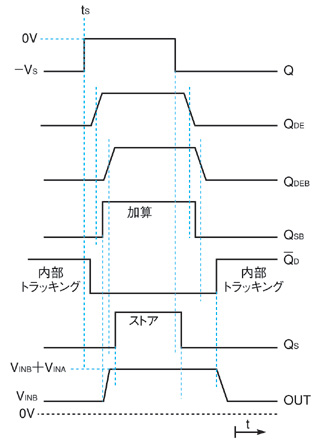

図1 2入力加算機能付きのSH回路 この回路では、2つの入力VINAとVINBがコンデンサC1とC2によって同時にトラッキングされる。これらのコンデンサに保持された電圧がサンプリング周期内で加算され、コンデンサC3に保持される。この回路には外付け抵抗を使用していない。また、オペアンプIC6、1個のNORゲート、デュアルのANDゲートによってロジック信号用のディレイラインを構成している。これにより、1つの外部ロジック信号Qから所要の内部ロジック信号を生成している(図2)。各ロジック信号がローになると、それに対応するフォロワアンプは遮断状態(ディセーブル)になり、その出力がハイインピーダンスとなる。

内部トラッキング期間、すなわちロジック信号QDがハイレベルにある期間では、フォロワアンプA1、B1、A2が動作状態(イネーブル)になる。それにより、一端がグラウンドに接続されたコンデンサC2が入力電圧VINAに充電される。また、コンデンサC1の下位側(IC2の2番端子側)はA2の働きによってグラウンドレベルになり、上位側(IC1の9番端子側)はB1によって入力電圧VINBに充電される。

ロジック信号QSBがハイになると、フォロワアンプB3がイネーブルになり、その結果、コンデンサC1の下位側の電圧が0Vから、直前にコンデンサC2に保持されていた電圧であるVINAに変化する。従って、コンデンサC1の上位側の電位は図2の一番下の波形に示すように、VINA+VINBに上昇し、2入力の加算が実現される。

サンプリングのタイミングを決めるロジック信号QSのローからハイへの変化をQSBのローからハイへの変化よりも少し遅らすことにより、出力にグリッチが発生するのを防ぐことができる。QSがハイのときには、IC2の7番端子への入力電圧、つまりVINA+VINBが、イネーブル状態のフォロワアンプB2を経由してコンデンサC3に入力され、次のサンプリングのタイミングまで保持される。

脚注

※1…『外付け抵抗が不要な2倍増幅SH回路』(Marian Stofka、EDN Japan 2008年3月号)

※2…"AD8592 Dual, CMOS Single Supply Rail-to-Rail Input/Output Operational Amplifier with ±250 mA Output Current and a Power-Saving Shutdown Mode," Analog Devices Inc, 1999.

Copyright © ITmedia, Inc. All Rights Reserved.

図2 各ロジック信号の波形とコンデンサC1上位側の電位 一番下の波形がコンデンサC1の上位側の電位の変化を表す。このノードの電位は、最初はVINBに等しくなり、QSBがハイになる期間でVINAとの加算値になる。

図2 各ロジック信号の波形とコンデンサC1上位側の電位 一番下の波形がコンデンサC1の上位側の電位の変化を表す。このノードの電位は、最初はVINBに等しくなり、QSBがハイになる期間でVINAとの加算値になる。