直列接続した複数のキャパシタを均等に充電:Design Ideas

電気2重層キャパシタを直列接続して充電する場合、各キャパシタの容量値の違い(ばらつき)によって、それぞれが異なる電圧に充電されてしまうという問題がある。

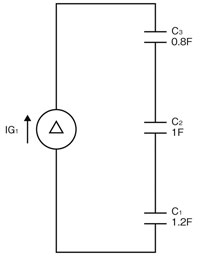

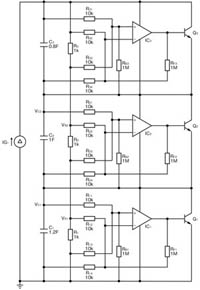

ここでは、±20%の誤差を持つ容量値1Fのキャパシタを例にとることにしよう。その場合、図1の回路のように0.8F、1F、1.2Fの3つのキャパシタを充電するのと同等の状況になり得る。この回路において、1Aの電流で5秒間充電を行うとしよう。

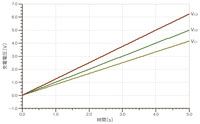

この条件で、各キャパシタの充電電圧をシミュレーションすると、図2のような結果になる。上から0.8F、1F、1.2Fのキャパシタが充電される電圧を表しており、それぞれに充電電圧が異なることがわかる。充電電流値I〔A〕で容量値がC〔F〕のキャパシタを充電する場合、充電電圧VC〔V〕は∫Idt/Cで表される。すなわち、充電電圧は容量値に反比例するため、違いが生じるのである。問題なのは、このまま使用すると、容量値の小さなキャパシタが最初に定格電圧に達してしまい、容量値の大きいキャパシタに十分な電荷を蓄えることができなくなることだ。

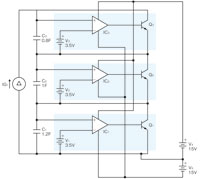

この問題の対策として、図3*1)に示した並列モニター回路(図の網掛け部分)を使用する方法がある。同回路を各キャパシタに並列に接続し、すべてのキャパシタが均等に定格電圧まで充電できるようにするのだ。

この回路の動作は、次のようになる。まず、キャパシタの実際の充電電圧と、目標となる充電電圧Vref(以下、均等電圧。図ではV1〜V3に相当)とを比較する。キャパシタC1〜C3のいずれかにおいて、実際の充電電圧がVrefを超えたら、各キャパシタに対応するトランジスタQ1〜Q3がオンになる。それにより、充電電流をバイパスすることで、キャパシタへの過充電を抑えるのである。

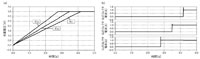

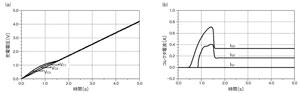

図4に、この回路の動作をシミュレーションした結果を示した。(a)は各キャパシタC1〜C3の充電電圧、(b)は各キャパシタに並列接続されたトランジスタQ1〜Q3のコレクタ電流(すなわちバイパス電流)である。図4の結果から、キャパシタへの充電が完了するまでコレクタ電流はまったく流れず、充電完了と同時にバイパス電流として大きな充電電流が流れることがわかる。すなわち、この方式を用いる場合、トランジスタQ1〜Q3としては大電力用のものを用いなければならないことが課題となる。

本稿で紹介するのは、この問題を解決する回路方式である(図5)。この方式では、直列接続するキャパシタと同じ数だけ同じ値の抵抗(R1〜R3)を直列接続し、その両端を充電器の両端に接続する。R1〜R3の抵抗値は等しいので、各抵抗の両端の電圧は等しくなる。この電圧(以下、均等電圧)とキャパシタの実際の充電電圧を比較し、両者が同じ値になるよう制御する。

この回路の動作シミュレーションの結果は、図6のようになる。(a)は各キャパシタの充電電圧である。オペアンプIC1〜IC3が動作し始める1秒くらいまでは図2と同じ状態になるが、各オペアンプが動作し始めると、それ以降は均等に充電されている様子が見て取れる。また、(b)は、上からそれぞれトランジスタQ3、Q2、Q1のコレクタ電流を表している。

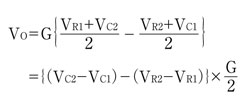

キャパシタC2を制御するオペアンプIC2を例にとり、この回路の動作原理を説明する。図において、抵抗R11〜R14、R21〜R24、R31〜R34の値は等しい。これらの抵抗の値は、R1〜R3のそれぞれに発生する均等電圧を乱さない程度に高くする。R1とR2の接続点の電位をVR1、R2とR3の接続点の電位をVR2とし、C1とC2の接続点の電位をVC1、C2とC3の接続点の電位をVC2とする。このとき、IC2の非反転入力端子の電位は、R21〜R24の抵抗値が同じなので(VR1+VC2)/2となり、反転入力端子の電位は(VR2+VC1)/2となる。IC2の出力電圧VOは、同オペアンプの利得をGとすると以下の式で表される。

すなわち、均等電圧(VR2−VR1)と、キャパシタの実際の充電電圧(VC2−VC1)を比較した誤差電圧が増幅されて、npnトランジスタであるQ2のベースに供給されることになる。従って、実際の充電電圧が均等電圧よりも低いとQ2はオフになる。一方、均等電圧より高いと、充電電圧が均等電圧になるよう不要な充電電流がQ2を介してバイパスされる仕組みである。

この構成では、オペアンプが動作し始めた瞬間のみ幾分多めの電流が流れる(シミュレーション結果で言えば、1.5s付近まで)。しかし、これについては、図3の回路と同様に、オペアンプに別電源を用いることで解消できる。そして、図6のとおり、バイパス電流は図1の回路と比較して小さくなり、小電力用のトランジスタが使用できる。また、発熱時間が分散されるため、放熱設計も容易になる。

回路について補足すると、まずRF1〜RF3は、それぞれオペアンプIC1〜IC3が不安定にならないように利得を下げる目的で付加している。また、RB1〜RB3は、すべてのキャパシタの充電電圧が均等電圧になったときに、充電電流のすべてがトランジスタQ1〜Q3を通してバイパスされ、キャパシタが充電されなくなるのを防ぐためのものである。IC1〜IC3の非反転入力端子の電圧をわずかに下げて、Q1〜Q3が同時にオンしてキャパシタへの充電が止まることを防止している。

なお、本稿の回路では示していないが、キャパシタが過充電に陥ってしまうのを避けるために、直列接続された全体の電圧をモニターし、規定の充電電圧に達したら、充電を止めるという制御を設ける必要がある。

脚注

※1…特許出願公開番号2008-271722。

Copyright © ITmedia, Inc. All Rights Reserved.