微細化に堪え得るオンチップSRAM:ワード線電位制御の効果を知る(2/3 ページ)

ワード線電位制御

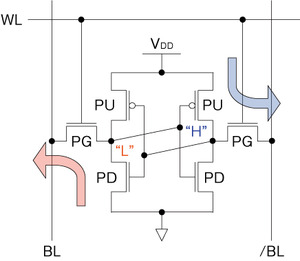

一般に、SRAMセルの設計では、読み出し動作と書き込み動作のバランスを考慮して各トランジスタの駆動力比を確保することが重要である。図6は、SRAMにおける読み出しと書き込みの動作の様子を表している。読み出し時には、プルダウン用nMOS(PD)の駆動力に比べて転送ゲートPGの駆動力が大きいほど、ワード線の選択時にフリップフロップ両端の電圧の浮きが大きくなる。そのため、ディスターブ不良が発生しやすくなる。一方、書き込み時にはビット線のいずれかがローになることでフリップフロップを反転させる。このとき、プルアップ用pMOS(PU)の駆動力に比べて転送ゲートPGの駆動力が弱いと、フリップフロップを反転させづらくなる。そのため、書き込み不良が発生しやすくなる。通常は、これらのトレードオフを考慮した最適な駆動力比となるように素子のサイズを設計する。

上述した各トランジスタの駆動力比(PD/PUとPGの駆動力比)を、チップの製造後に調整可能にする方法がある。それが、本稿で取り上げるワード線電位制御である。

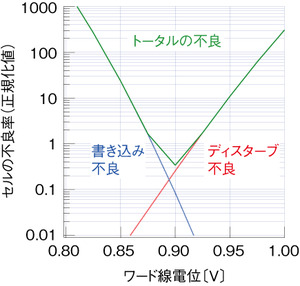

図7に、ワード線の電位を変えた場合のメモリーセルの不良率の変化を示した。ワード線の電位が低い場合、転送ゲートPGの駆動力が小さくなるので、書き込み不良が支配的となる。一方、ワード線の電位が高い場合にはディスターブ不良が増加する。そして、ワード線電位を最適な値に設定すれば、トータルの不良率を最小にすることが可能になる。

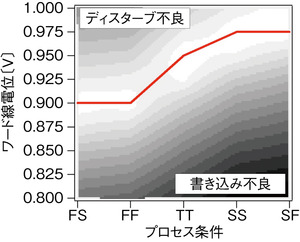

さらにプロセス変動も盛り込むと、ワード線電位の変更により図8に示すような結果が得られる。横軸は、nMOS、pMOSがそれぞれFast(速い)、Typical(標準)、Slow(遅い)のいずれのプロセス条件にあるかを示す。例えば、「FS」はnMOSがFast側に、pMOSがSlow側にシフトした条件を表している。また、等高線は不良率を表し、色が明るいほど不良が少ないという意味である。

各素子の駆動力比は、プロセス条件に応じて変動する。従って、不良率が最小になる最適なワード線電位はプロセス条件によって異なる。通常のSRAMでは、ワード線の電位は固定(=電源電圧)なので、あらかじめあらゆるプロセス変動を考慮して最適値となるようにセルを設計する。

一方、ワード線の電位を制御することにより、各プロセス条件に応じてワード線の電位を最適な値に設定するようにすれば、各チップのSRAMを不良率が最小となる部分(図8の赤色の部分)で動作させられるようになる。このようなプロセス変動に応じたワード線電位制御により、セルの不良率は大幅に改善する。その分、チャンネル面積を縮小することが可能になる。

具体的な回路構成

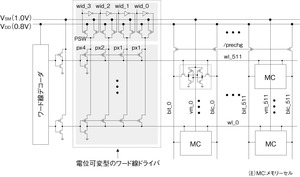

次に、ワード線電位制御を行うための具体的な回路構成について説明する。近年のハイエンドICでは、SRAM専用の電源を導入した設計が多く見受けられる*4)。具体的には、通常のロジック用電源よりも200mVほど高いSRAM用電源を使用する。これは、ロジック用電源の電圧をSRAMの動作下限電圧よりも下げて、チップ全体の消費電力を減らすことを目的としている。これら2つの電源を利用することで、ワード線の電位を両電源間の任意のレベルに設定することができる。

図9に、ワード線電位制御を利用したSRAMの回路構成を示した。図中の電位可変型のワード線ドライバは、ワード線を駆動するためのインバータ回路である。この回路では、ワード線をプルアップするpMOSが並列に分割して配置されている。そして、各pMOSのソース端子に、2つの電源のうちいずれを供給するかを選択できるようになっている。すなわち、通常のロジック用電源VDDが供給されたpMOSと、ロジック用電源よりも高いSRAM用電源VSMが供給されたpMOSが並列に接続された構成となる。これにより、2つの電源間をpMOSで抵抗分割したようなかたちとなり、ワード線の電位はVDDとVSMの間の値になる。その値は、VDDの供給されたpMOSと、VSMの供給されたpMOSの駆動力比に応じて変更できる。

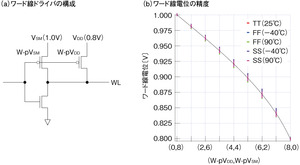

この駆動力比は、それぞれの電源が供給されるpMOSのチャンネル幅によって決めることができる。図10(a)は、チャンネル幅の異なるワード線ドライバの概念図である。一方、図10(b)はVDDが供給されたpMOSのチャンネル幅W-pVDDと、VSMが供給されたpMOSのチャンネル幅W-pVSMの比を変えた場合に、ワード線電位がどのように変化するかを示している。このように、チャンネル幅の比に応じてワード線の電位が変化することを利用すれば、製造後にプロセス条件を判定し、各SRAMに適切なワード線電位を設定することが可能になる。具体的には、レーザートリミングなどの手法により、図9で言えばwid_3〜wid_0の信号の設定を行えばよい。

このワード線電位の生成方法のメリットは、プロセス、温度などの条件が変わっても、ワード線レベルの変動幅が±10mVと小さいことである。ワード線ドライバに用いるpMOSは、メモリーセルよりも寸法が大きいので、局所ばらつきの影響はそれほど大きくない。特性のそろったpMOS同士のチャンネル幅比でワード線レベルが決まるため、変動幅を抑えられるのである。図7に示したように、SRAMセルの不良率は、ワード線の電位に対して敏感であるため、変動幅を小さくすることが重要なポイントとなる。

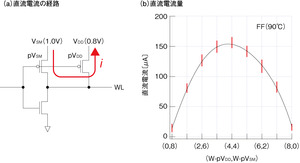

一方、この方法の問題点としては、消費電流が増加することが挙げられる。pMOSにより抵抗分割のようなかたちで中間レベルの電位を生成するため、ワード線の選択時に、2つの電源間に直流電流が発生するからである。前ページの図11(a)がその電流経路であり、図11(b)は直流電流量を表している。この直流電流は、2つの電源のちょうど中間程度の電位を生成しようとした場合に最大になる。とはいえ、動作時以外にはこの電流は発生せず、通常は、全体の動作電流と比べて問題にならない程度(200μA以下)だと考えられる。ただし、用途などによっては注意が必要である。

脚注

※4…G. Gammie, et al., "A 45nm 3.5G Baseband-and-Multimedia Application Processor using Adaptive Body-Bias and Ultra-low-Power Techniques," ISSCC Dig. Tech. Papers, pp.258-259, Feb. 2008

Copyright © ITmedia, Inc. All Rights Reserved.