FPGA検証のコツ:ビデオ処理システムの例で知る(2/2 ページ)

周辺デバイスの検証

ストリーミングメディアの急速な進歩で、システムにはより一層の高速動作が求められている。高速に動作するFPGAシステムでは、周辺デバイスの実装について注意が必要だ。周辺デバイスには、入力セットアップ‐ホールド時間のタイミングに制約があり、検証エンジニアは、すべての周辺デバイスにおける制約を把握する必要がある。さまざまなタイミング制約を持つFPGAを検証するための装置として、オシロスコープを活用するのも1つの方法だ。

FPGAには、UART(Universal Asynchronous Receiver/Transmitter)、I2C、SPI(Serial Peripheral Interface)、GPIO(General Purpose Input/Output)など、標準のインターフェースに対応したポートが実装されることがある。こうしたポートの検証方法は、規格ごとに変える必要がある。カスタムインターフェースを使用する場合も、周辺デバイスのタイミング制約について考慮しなくてはならない。例えば、FPGAのGPIOインターフェースがオンボードのマルチプレクサと接続されている場合、FPGAはマルチプレクサの選択入力を駆動し、その出力をキャプチャすることになる。マルチプレクサは、一度選択入力が変わると、出力のセトリングに時間を要する。検証モデルからの応答を生成する際に、その遅延を実現できるようにしておけば、マルチプレクサの出力が安定してからFPGAにキャプチャさせることを保証することができる。

実使用時に近付ける

検証の対象となるFPGA回路には、実使用時のソフトウエアアプリケーションを用いた検証フローを適用するとよいだろう。検証用のテストベンチでは正しく動作しているFPGAが、ソフトウエアアプリケーションによって何らかの制約が加わると、うまく動作しないというケースがあるからだ。

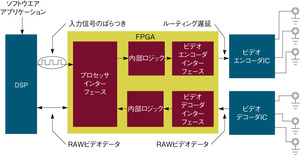

ここで、高解像度ビデオデータをキャプチャするFPGAの設計について考えてみよう(図1)。FPGAは、RAWビデオデータ(何も処理を施していないビデオデータ)をキャプチャし、内部のFIFO(First in, First out)バッファに取り込む。外部メモリーインターフェースにおいてFPGAとやり取りするDSPは、FPGAのFIFOからビデオデータを読み込んでキャプチャする。検証エンジニアは、実際のソフトウエアアプリケーションにおけるタイミング情報を使用することで、FIFOバッファが2連続で読み込みを行う場合に、DSPが要する時間の最大値を予測することが可能になる。また、そのDSPの制約を考慮したテストケースを作成することができるようにもなる。FIFOバッファが小さ過ぎて、最大間隔時間中に到着するすべてのデータをバッファできない場合には、テストでエラーが記録される。

通常、ビデオ信号処理で起こり得る問題は、データに依存する。従って、ボードの立ち上げ時には、異なる種類のデータパターンを使用することが重要である。それにより、任意のビデオストリーミングアプリケーションにおいて、正確なビデオ処理が行われることを確認することが可能になる。

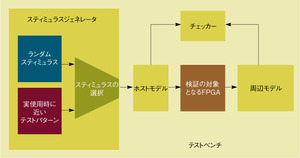

最近では、RAWデータ形式でそのようなテストパターンを生成できるようなオープンソースソフトウエアを入手することができる。検証エンジニアは、そうしたソフトウエアを用いることで、あるいはシステムからパターンを直接取得することによって、ビデオパターンをRAWデータファイルとして生成することが可能である(図2)。この手法により、検証エンジニアは、実使用に近いテストのシナリオを基に設計上の不具合を検出し、修正できる。システムで問題が起きるパターンを顧客が適用してしまう前に、対策できるというわけだ。

検証チームおよびソフトウエアチームは、設計サイクルの最初の段階で、テスト計画における共通のテストシナリオの集合を共有する必要がある。これにより、ボードの立ち上げ中に問題が生じないようにすることが可能になる。また、設計者は設計サイクルの初期段階において、実装または集積の誤りを検出し、修正が行えるようになる。

FPGAの設計は複雑であるため、設計者は、できる限り設計サイクルの初期の段階で問題を検出して、再スピンを避ける必要がある。ボードの立ち上げ時に生じる不具合の数を低減する上で、検証の役割は重要になってきている。システムアーキテクチャを慎重に検討することにより、検証エンジニアは、より実使用時に近いテストシナリオを記述することができる。そのシナリオに沿ってテストを実施することが効果的な検証作業につながり、最終的にはボードの立ち上げを容易にするのである。

Copyright © ITmedia, Inc. All Rights Reserved.