第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編):FPGA Insights

本連載では、FPGAを有効に利用してもらうために、基本的な「設計開発フロー」や「DDR2 SDRAMの実装からデバッグ手法」について、わかりやすく解説してきた。今回より、産業用ワイヤレスネットワークの構築に有効なFPGAの応用事例を紹介する。本稿では、産業用途向けワイヤレス通信規格である「WirelessHART」または 「SP100.11a」に対応した、柔軟性の高い通信インタフェース機能を工場内ネットワーク機器に実装するためにFPGAを応用した例について、前編と後編の2回に分けて解説する。

情報系のネットワーク・プロトコルとして広く普及している「イーサネット」だが、近年、生産現場においても導入が本格化しつつある。しかし、現実には複数の通信プロトコルが存在している産業用イーサネットをベースとしたネットワークに、各種フィールド機器を接続しようとすると、通信プロトコルの組み合わせが複雑となり、これらのネットワークをブリッジするICの開発には多大な労力が必要となる。

工場などの生産現場で用いられる制御系の通信は、これまで主要な企業や産業用ネットワーク団体が開発した独自のプロトコルを使った、クローズドなネットワーク環境で行われていた。しかし、独自のネットワークではもはやデータ転送速度の進化が市場のニーズに追従できないなどの問題に直面している。このため、生産現場でもイーサネットをベースにしたネットワークの導入機運が高まってきている。イーサネットは、一般的なオープン規格のネットワーク技術であり、技術進歩が著しく、データ通信速度もその技術進歩に合わせて高速化が進んでいるためだ。

「産業用イーサネット」とひとことでいっても複数の規格が提案されている。各規格とも、開発された背景の違いによって特徴がある。例えば情報系、制御系にフォーカスした規格や、モーション制御系をターゲットにした規格などさまざまだ。主な規格だけでも次のような規格があげられる。

- 日本電機工業会(JEMA)が規格化を推進する「FL-net(OPCN-2)」、

- CC Link協会が推進する「CC Link」

- Modbus-IDAが推進団体となる「Modbus/TCP」、

- SERCOS Internationalが推進母体の「SERCOS III」、

- EPSGが推進団体の「ETHERNET Powerlink」、

- ETGが推進団体となる「EtherCAT」、

- PI (PROFIBUS & PROFINET International) が提唱する「PROFINET」、

- ODVAとCIが推進団体の「EtherNet/IP」

- MECHATOROLINK協会が推進する「MECHATOROLINK-III」

一方で、信頼性を重視する産業用途でも、ワイヤレス通信への期待が高まっている。各種センサーをワイヤレスでつなぐ「ワイヤレスセンサーネットワーク」は、これからのユビキタスネットワーク社会を支える技術の1つとして注目されている。有線に比べて信頼性の問題を指摘する技術者はいるが、産業用途でも「コスト」や「敷設期間(配線作業が不要)」、「ネットワークの柔軟性」といった点が評価されている。

IEEE802.15.4をベースとした産業用ワイヤレス通信規格として代表的な3規格をあげる。「Wireless-HART」は、米国のHART Communication Foundationが提唱する無線通信用の計装通信プロトコルで、2010年3月にIEC(国際電気標準会議) から国際標準(IEC 62591Ed. 1.0)として承認された。「SP100」はISA(国際計測制御学会)のISA100委員会が2009年4月に認証したワイヤレス通信のデータバスプロトコルである。これ以外でも、ワイヤレスセンサーネットワークの技術標準化業界団体「ZigBeeアライアンス」が提唱する「ZigBeeネットワーク」などがある。

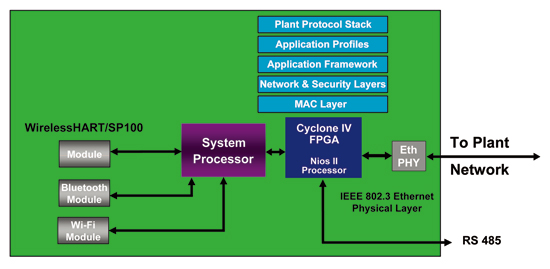

多岐にわたる産業用ネットワーク・プロトコルに対応可能なソリューションは、FPGA、組み込みプロセッサ、IP(Intellectual Property)コア、ソフトウエアプロトコルスタックなどを使うことによって実現することが可能である。図1は、ネットワークマネージャ / ゲートウェイシステムの回路ブロックの一例である。ここでは、アルテラ社のFPGAを使った回路ブロックを紹介する。ワイヤレス通信を行うフィールドネットワーク用無線モジュール、コアとなるシステムプロセッサ、FPGAに実装されたソフト・プロセッサ「Nios II 」(www.altera.co.jp/nios2?WT.mc_id=te_ba_er_nj_tx_4_131)を使った通信コプロセッサなどで構成される。FPGAは、ネットワーク管理や通信セキュリティの確保といったさまざまなタスクを処理するために、コアシステムプロセッサを解放できる柔軟性の高いプラットフォームといえる。

汎用産業用イーサネットソリューションの実装における課題

工場で採用されている複数の産業用イーサネット・プロトコルをすべてサポートするには、各プロトコルに対応できるプラグインボードをそれぞれ作成すれば実現することができる。しかし、世界中でいくつもの規格に準拠したネットワークが導入され、それらの規格が絶えず進化していることを考えると、このような対応ではターンアラウンドタイムの短縮もコスト低減の効果も期待することができない。

例えば、既存のCPUを使った場合、新しい機能/プロトコルのサポートに必要なパフォーマンス/ハードウエア要件を満たすことができなかったり、標準のプロトコルスタックを外部から入手することができなかったりする場合がある。逆に、新しいプロセッサ/スタックをサポートするために、現行のソフトウエアを再コーディングすることになれば費用や時間がかかりすぎる。その上、新しいCPUや産業用イーサネット向けASIC/ASSPチップを使えば、それに対応した新しい回路基板を開発する必要がある。産業用イーサネット・プロトコルがそれぞれ進化するたびに新しいハードウエアが必要となれば、バージョンが異なる複数の回路基板を事前に用意して、ASIC/ASSPチップの陳腐化に備えておくことが必須となる。このようなソリューションでは費用がかかるうえにサポートが難しく、新機能の開発期間が長くなる可能性が高い。

FPGAとPHYですべてを実行

こうした課題を解決する方法の1つがFPGAの活用である。柔軟性の高いFPGAを使用すれば、複数の産業用イーサネット規格に対応した回路基板を設計することができる。FPGAは回路の再構成が容易なため、製品の出荷直前まで、あるいは出荷後でも必要な回路を再プログラムするだけで、別のさまざまな産業用イーサネット・プロトコルに対応することができる。しかも、必要なFPGAコンフィギュレーションファイルがあれば、この作業はわずかな時間(数秒)で簡単に行うことができる。

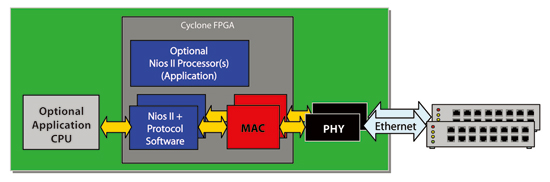

FPGAは、イーサネット・トランシーバ(PHY)と組み合わせることで、イーサネット・インタフェースで要求されている機能をすべて実行できる。メディアアクセスコントローラ(MAC - レイヤ2)機能はプログラマブルFPGAロジックで実現する。上位機能(レイヤ3以上)はプロセッサコアで実行されるソフトウエアで実装すると同時に、FPGAロジックを使用して構成する。「FPGAロジックのプログラムが容易である」、「I/Oピンで複数の規格がサポートされる」、「幅広いインタフェースIPを入手できる」ことから、既存のアプリケーションプロセッサとFPGA間の通信チャンネルを実装するのも容易である。大抵の場合、FPGAとの通信には、プロセッサデバイスの既存の通信機能(I2C、SPI、あるいは他のローカルパラレルバスなど)またはシステムの通信機能(PCI、PCI Express、CANopenなど)を使うことができる。このアプローチには、演算時間および既存プロセッサ上で実行されるアプリケーション・ソフトウエアへの変更を最小限に抑えられるという、別のメリットもある。

FPGAでは、2個以上のソフト・プロセッサコアを内蔵したシステムを簡単に開発することができる。必要であればアプリケーションの処理機能をFPGAに統合することも可能である(図2)。このようなシステム統合によってゲートウェイに実装する部品数や部品コストを削減し、同時に電力消費量を軽減できる。さらに、今では設計が完全にIPベースになっていることから、設計資産を次世代FPGAに移植することも容易である。

FPGAであれば、新しいインタフェースをシステムに実装することも可能だ。単純な通信インタフェースから、新しいメモリ規格(DDR2/3 SDRAMインタフェースなど)や最新の通信技術(Bluetooth、PCI Expressなど)をサポートする複雑な通信インタフェースまで、その選択肢は幅広い。

後編では、FPGAベースの設計フローやIPコアの活用事例などについて解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。