Xilinx社が新パッケージ技術を開発、28nmの「Virtex-7」は4ダイ構成に

米Xilinx社は2010年10月、東京都内で会見を開き、28nmプロセスを用いたFPGA「Xilinx 7シリーズ」に採用するパッケージング技術「スタックド シリコン インターコネクト(SSI)」を発表した。同社は、2011年末にSSIを用いた試作サンプル品の提供を開始する予定。ロジックセル数が約200万個の「Virtex-7 LX2000T」をはじめ、回路規模が大きい5品種の「Virtex-7」にSSIを適用する計画である。

同社は、2011年1〜3月期から、Xilinx 7シリーズの市場展開を開始することを表明している。Xilinx 7シリーズには、ハイエンドのVirtex-7、ミドルレンジの「Kintex-7」、普及価格帯の「Artix-7」の3つのファミリがある。これらのうち、Virtex-7のロジックセル数は、現行製品の中で最も性能が高い「Virtex-6」の2.6倍に当たる約200万個まで拡大するとしていた。

ここで問題になるのが、約200万個のロジックセルに加えて、高機能のDSPや大容量のメモリーなども集積したFPGA製品を量産する際に、その製造歩留りをどこまで高められるのかということである。Xilinx社のシニアマーケティングマネジャを務めるDavid Myron氏は、「初期の28nmプロセスでは、Virtex-7クラスの大規模の回路を1個のダイに集積しようとすると、その歩留りは非常に低くなってしまう。量産に耐え得る一定の歩留りを確保するには、ダイのサイズを小さくしなければならない。しかし、ダイのサイズを小さくすると、必要とする規模の回路を集積できなくなる。そこで、当社は、ダイの大きさは一定の歩留りを確保できるレベルにとどめ、複数のダイを1つのパッケージに収める方法により、大規模な回路の集積を実現するパッケージング技術を開発した。それがSSIだ」と語る。

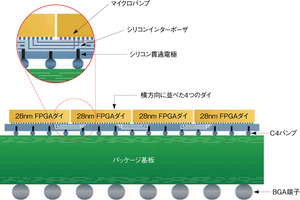

SSIは、主に4つの技術から構成されている(図1)。1つ目は、個々のFPGAダイの端子となるマイクロバンプである。マイクロバンプの幅は25μm、バンプ間の距離は45μm。1個のダイにつき、1万個以上のマイクロバンプを形成する。なお、マイクロバンプの製造技術は、CMOSイメージセンサーなどで利用実績があり、「歩留りを大幅に低下させる要因にはならない」(Myron氏)という。

2つ目は、ダイ−ダイ間、ダイ−パッケージ基板間を接続する役割を担うシリコンインターポーザである。シリコンインターポーザの厚さは100μm。内部の配線層は、65nmプロセスを用いて製造されており、層数は4、配線幅は10μmとなっている。インターポーザの内部にトランジスタなどの能動素子は一切搭載していないことから、Xilinx社は「パッシブ(受動)シリコンインターポーザ」と呼んでいる。

3つ目に挙げられるのが、シリコンインターポーザとパッケージ基板を接続する部分に利用されているシリコン貫通電極(TSV)技術だ。各ダイの電源、グラウンド、I/O端子に対応する入出力信号は、インターポーザの配線層を経由して、インターポーザの下側に形成された貫通電極に集約される。そして、貫通電極の下側に形成された幅100μmのC4(Controlled Collapse Chip Connection)バンプを用いて、パッケージ基板と接続する。ICとしての入出力は、パッケージ基板の下部に形成されたBGA端子を用いることになる。

4つ目は、パッケージに搭載するダイを横方向に配列した設計である。Xilinx社がSSIを初めて適用するVirtex-7 LX2000Tでは、縦長のダイを横方向に4個並べて接続する。なお、各ダイには、ロジックセルやDSP、メモリー以外にも、回路の設定を行うためのコンフィグレーション回路も集積されている。Xilinx社によれば、「Xilinx 7シリーズでは、3つの製品ファミリに対して、共通のロジックファブリック、ブロックRAM、DSPスライスなどを用いながら、それらを異なる割合で組み合わせることにより、想定されるアプリケーションに合わせて最適化するアーキテクチャを採用している。このアーキテクチャがなければ、最終的なFPGA製品の回路規模を4個の同じダイに分割することはできなかった」という。

Xilinx社で上級副社長兼CTO(最高技術責任者)を務めるIvo Bolsens氏は、「SSIを用いてFPGAダイを接続する場合、標準的なI/OやSERDES(シリアライザ/デシリアライザ)を用いてFPGAパッケージ間を接続して運用する場合よりも、広い帯域幅が実現できるし、遅延時間(レイテンシ)や消費電力も少なくすることができる」と強調する。例えば、FPGAパッケージを標準的なI/OやSERDESで接続する場合と比べて、SSIでFPGAダイを接続する場合の消費電力1W当たりの帯域幅は100倍に達するという。つまり、低消費電力で高速の処理能力を実現できる28nmプロセスの優位性が、SSIによって損なわれることはないということである。また、SSIで接続したFPGAダイ間のレイテンシは約1nsと非常に小さい。さらにBolsens氏は、「SSIを適用することにより、競合他社の28nmプロセスを用いたFPGA製品よりも、約2.8倍のロジックセル数を確保できるようになった」と述べている。

なお、Xilinx社が、SSIを用いて製造を行う際のサプライチェーンは以下のようになっている。FPGA、インターポーザ、パッケージの設計と、最終的なパッケージレベルでの試験はXilinx社が担当する。28nmプロセスを用いたFPGAダイとインターポーザの製造は、台湾TSMC(Taiwan Semiconductor Manufacturing Company)社が行う。パッケージ基板はイビデンが提供する。FPGAダイへのマイクロバンプの形成からパッケージングまでの工程は、台湾Amkor Technology社が担当する。

SSIのように複数のダイを用いる場合、FPGAの回路構成を設定する開発ツールの対応も必要になる。Xilinx社の開発ツール「ISE Design Suite」では、2011年中ごろに一般公開を予定しているバージョン13.1から、複数のダイで構成されるFPGA製品のサポートを開始する予定である。同バージョンでは、ダイが複数あることを意識せずに回路の割り当てを行える簡便な「プッシュボタンフロー」などの機能が用意されている。

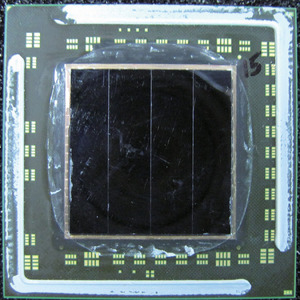

会見では、28nmプロセスで製造した4個のFPGAダイをSSIで接続した試作品を披露した(写真1)。Xilinx社は、SSIの技術実証を目的として、2008年の後半から90nmプロセスで製造したFPGAダイを用いた試作品を開発し、2009年の中ごろから40nmプロセスで製造したFPGAダイを用いた試作品を開発している。28nmプロセスの試作品は2009年後半から開発しているものである。

SSIを適用した初の量産品となるVirtex-7 LX2000Tについては、2011年末に試作サンプルの提供が開始される予定である。なお、2011年1〜3月期に市場投入されるXilinx 7シリーズの製品は、1個のダイで構成される比較的回路規模の小さい製品となる見込みだ。

(朴 尚洙)

Copyright © ITmedia, Inc. All Rights Reserved.