第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜:FPGA Insights

パソコン本体と周辺機器やUSBメモリなどを接続するための次世代インタフェースとして、最大5Gビット/秒のデータ転送速度を実現する「USB3.0」が注目を集めている。本連載では低コストFPGAを使うことで、USB3.0インタフェースを低リスクで、容易に実現することができるソリューションについて紹介してきた。本稿では、USB3.0インタフェースの開発/検証に用いたアルティマ製ボード「Cyclone III USB3.0 Board」のベンチマーク測定の結果について解説する。

これまで、「ステップ1」と「ステップ2」で、USB3.0インタフェースの概要や基板設計のガイドラインなどを述べてきた。USB3.0インタフェースは、現行のUSB2.0インタフェースに比べて通信速度が約10倍と高速である。また、大容量の画像データを高速伝送するのに適したBurst転送機能なども新たに追加されている。このため、USB3.0インタフェースは、放送用カメラ、記憶装置、FAカメラなどへの搭載に期待が高まっている。しかし、下位互換性を確保しつつ、次世代インタフェースとして性能や機能が大幅に向上したことで、回路設計者にとってはUSB3.0インタフェース回路を設計する際の難易度も高まった。

こうした中で、機器設計者は、開発リスクを抑えつつ低コストで、早期にUSB3.0インタフェースを開発することが求められている。ステップ1でも述べたが、USB3.0インタフェースを実現する手段としては、「ブリッジASSP」や「フル機能を取り込んだASIC」を開発/採用するか、「FPGAとPHYチップの組み合わせを利用した開発」といった方法がある。現時点では機器設計者の要求に応えられるUSB3.0対応の専用チップが簡単に入手できる状況ではなく、機器メーカー側で独自に開発するケースが多いようだ。

このような技術者に向けて、USB3.0インタフェース開発における課題を解決する手法の1つとして、本連載では低コストFPGA「Cyclone III 」を用いたUSB3.0ソリューションを取り上げてきた。今回のステップ3では、これまでステップ1やステップ2で紹介してきたCyclone III USB3.0 Board(写真1)の性能について、ベンチマーク用ソフトウエアや各種測定器を使って実施した評価テストの結果を紹介する。

Cyclone III USB3.0 Boardのベンチマーク測定を行うに当たって、ホスト(PC)側のPCIe Gen2レーンに、PCIe to USB3.0のホストボードを実装した。その上で、Cyclone III USB3.0 Board をUSB3.0ケーブルでホスト側と接続し、ホスト側にはマスストレージ・クラスとして認識させた。

検証環境のシステム構成は、CPUが「Intel Core i7 9200」、OSが「Windows XP sp3」で、メインメモリは3Gバイトを実装した。ドライバソフトとしてはWindows標準マスストレージドライバを使い、ホストボードは「IFC-PCIE2U3」を用いた。さらに、USB3.0インタフェースの開発/検証に必須となるプロトコルアナライザはEllisys社の「USB EXPLORER 280」を、ベンチマーク測定ツールとしてはフリーツールの「CrystalDiskMark3.0」をそれぞれ使った。

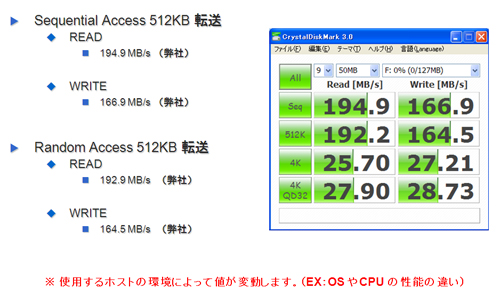

IN転送で194.9MB/s、OUT転送で166.9MB/s

USB3.0インタフェースは、使用するホスト環境によってもその転送速度の数値は異なる。上述の検証環境で行った結果を図1に示す。「Sequential Access(512kバイト転送)」の場合、読み出し(READ、IN転送)で194.9Mバイト/秒、書き込み(WRITE、OUT転送)で166.9Mバイト/秒となった。「Random Access(512kバイト転送)」の場合だと、読み出しで192.9Mバイト/秒、書き込みで164.5Mバイト/秒となった。今回は特殊なドライバソフトウエアは開発しておらず、すでにWindowsに実装されている標準マスストレージドライバをそのまま使った。

専用のドライバソフトウエアを用意するなど最適化を図ることで、転送速度はさらに改善される。ちなみに、USB2.0インタフェースの転送速度は、読み出しが約21Mバイト/秒、書き込みが約5Mバイト/秒というのが一般的のようだ。

「Command」と「Status」がオーバーヘッド

ここで、マスストレージ・クラスのデータ転送方式について紹介する。マスストレージ・クラスは、「Command」、「DATA」、「Status」の順番でデータ転送が行われるため、「Command」と「Status」の分だけオーバーヘッドが大きくなる。

IN転送を解析した結果では、「Command」と「Status」間(1Block)の転送速度は268Mバイト/秒となる。DATAのみを1パケットとすれば、その転送速度は329Mバイト/秒となる。1Blockを3回繰り返した場合のデータ転送速度は188Mバイト/秒である。

OUT転送では、「Command」と「Status」間の転送速度は236Mバイト/秒、DATAのみ転送すると244Mバイト/秒、1Blockを3回繰り返した場合のデータ転送速度は161Mバイト/秒となった。

IN転送、OUT転送のいずれの場合も、Windows XPのウィンド・サイズにより、データは64kバイト/秒(64パケット)となり、64kバイトの転送後のウエイトがボトルネックとなる。

今回は、ベンチマーク測定ツールを使ってCyclone III USB3.0 Boardの実力を探った。次回のステップ4では、Cyclone III USB3.0 Boardと、市販されている2種類のホストボードおよび3種類のマザーボードを使って実施した接続確認の実例を挙げ、接続不具合を生じた際の検証項目や原因解明の手法などについて解説する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第11回 FPGAの設計開発フロー:〜ステップ1 デザイン設計〜

第12回 FPGAの設計開発フロー:〜ステップ2 制約設定〜

第13回 FPGAの設計開発フロー:〜ステップ3 コンパイル〜

第14回 FPGAの設計開発フロー:〜ステップ4 プログラミング〜

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●アルティマ、国内初*「低コストFPGAで実現するUSB3.0ソリューション」を発表[プレスリリース]

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。