「MATLAB」ファイルからHDLコードを直接生成、新オプションでHDL対応を拡充:MathWorks HDL Coder/HDL Verifier

モデルベース設計環境「MATLAB/Simulink」の新バージョン「R2012a」の発表に合わせて、HDLに対応する新オプションが2つ追加された。「HDL Coder」は「MATLAB」ファイルからのHDLコードを自動生成が可能。「HDL Verifier」は、MATLABファイルや「Simulink」モデルに加えて、手書きのHDLコードをFPGAの評価ボードに実装して、検証作業を行うことができる。

The MathWorksは2012年3月、同社のモデルベース設計環境「MATLAB/Simulink」に、FPGAやASICの設計に広く利用されているHDL(ハードウェア記述言語)に対応する新たなオプションを2つ追加すると発表した。1つは、技術計算ソフトウェアである「MATLAB」で記述したファイル(以下、MATLABファイル)からHDLコードを自動生成できる「HDL Coder」である。もう1つは、MATLABファイルや「Simulink」モデルをFPGAの評価ボードに実装して、ハードウェアベースの検証作業を実施できる「HDL Verifier」である。両オプションとも、同日に発表したMATLAB/Simulinkの新バージョン「R2012a」から利用できる。価格は、HDL Coderが135万円から、HDL Verifierが42万5000円から。

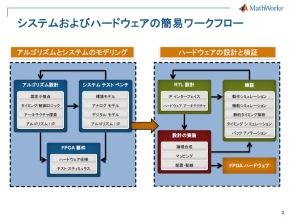

同社によれば、最近の電子機器の設計開発フローにおいて、上流に位置するアルゴリズムとシステムのモデリングを行う技術者と、そのアルゴリズムやシステムモデルに基づいてハードウェアの設計と検証を行う技術者の間では、それぞれが所属する部門や企業、拠点などが異なるために、コミュニケーションが取りづらい状態にあるという。このような分断された開発体制では、もし最終的なハードウェアの検証で不具合が見つかっても、どちらの工程に不具合の原因があったのかを早急に把握できないので、不具合修正の作業に時間がかかってしまう。日本法人のMathWorks Japanでインダストリーマーケティング部のシニアマーケティングスペシャリストを務める柴田克久氏は、「今回発表したHDL対応のオプションは、アルゴリズム設計で広く利用されているMATLABファイルからHDLコードを自動生成したり、MATLABファイルをFPGAの評価ボードを使って検証したりすることが可能だ。これにより、アルゴリズム設計を担当する技術者とハードウェア設計を担当する技術者との間でコミュニケーションを取りやすくなるので、開発期間の短縮につなげられるだろう」と語る。

左の写真はMathWorks Japanの柴田克久氏。右の図は電子機器の設計開発フローである。「HDL Coder」と「HDL Verifier」によって、アルゴリズム設計(図内左側)とハードウェア設計(図内右側)の間でコミュニケーションを取りやすくなる。(クリックで拡大) 出典:MathWorks Japan

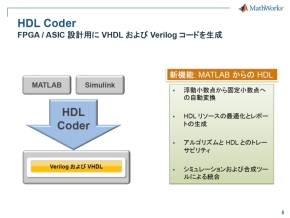

左の写真はMathWorks Japanの柴田克久氏。右の図は電子機器の設計開発フローである。「HDL Coder」と「HDL Verifier」によって、アルゴリズム設計(図内左側)とハードウェア設計(図内右側)の間でコミュニケーションを取りやすくなる。(クリックで拡大) 出典:MathWorks JapanMathWorksはこれまで、Simulinkで作成したモデルからHDLコードを自動生成するオプション「Simulink HDL Coder」を提供していた。HDL Coderは、このオプションを、MATLABで記述したファイルから直接HDLコードを自動生成できるように拡張したものである。生成できるHDLコードは、VerilogとVHDLの2種類。また、HDLコードの出力データを計測するためのテストベンチを自動生成する機能も備える。さらに、Xilinx、Altera、Mentor Graphics、Synopsysの論理合成ツールに用いるスクリプトの生成も可能だ。

HDL Coderを利用する際には、C言語の自動生成オプション「MATLAB Coder」と、MATLABで固定小数点を使ったプログラミングを行うのに用いる「MATLAB Fixed-Point Toolbox」が必要である。柴田氏は、「MATLABで記述したアルゴリズムは、浮動小数点で数値を扱っている。一方、HDLは、固定小数点で数値を扱うことが多い。つまり、MATLABファイルからHDLコードを自動生成するには、数値を浮動小数点から固定小数点に変換する機能が必須になる。HDL CoderとMATLAB Fixed-Point Toolboxの機能を使えば、浮動小数点から固定小数点への変換を簡単に行える」と説明する。

この他、HDL Coderは、ベースとなったSimulink HDL Coderと同様に、SimulinkモデルからHDLコードを自動生成する機能も備えている。

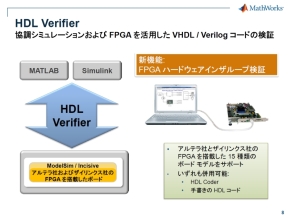

一方、HDL Verifierは、MATLAB/SimulinkとEDAベンダーの論理シミュレータを連携させる際に用いるオプション「EDA Simulator Link」がベースとなっている。HDL Verifierは、論理シミュレータとの協調動作に加えて、XilinxとAlteraのFPGAを搭載した評価ボードを用いて動作試験を行うHILS(Hardware in the Loop Simulation)検証にも対応している。現時点でHDL Verifierがサポートしている評価ボードは、Xilinxの「Spartan-6」を搭載する「SP605」や、Alteraの「Cyclone IV」を搭載する「Cyclone IV GX FPGA development kit」など、接続インタフェースとしてイーサネットを備える15品種である。

HDL Verifierは、MATLABファイルやSimulinkモデルの他に、専用の関数を用いてプログラミングを行えるオプション「System Objects」(関連記事)を利用したMATLABファイルにも対応している。論理シミュレータについては、EDA Simulator Linkと同様に、Mentorの「ModelSim」と「Questa」、Cadence Design Systemsの「Incisive Enterprise Simulator」に対応している。Synopsysの「VCS」については、「現時点では対応する予定はない」(柴田氏)という。

また、HDL Verifierは、HDL Coderで自動生成したHDLコードの他に、手書きのHDLコードを使ったHILS検証も可能である。手書きのHDLコードが使えるということは、FPGAベンダーが提供する純正品以外のツールで作成したHDLコードについても、上記の15種類の評価ボードに搭載されているFPGAへの実装が可能になることを意味する。柴田氏は、「従来、FPGAの評価ボードにHDLコードを実装するには、Xilinxの『System Generator』やAlteraの『DSP Bulider』などFPGAベンダーの純正ツールが必要だった。MATLAB/SimulinkとHDL Verifierを使えば、サードパーティのツールで作成したHDLコードを実装できるようになる」と述べている。

関連キーワード

MATLAB/Simulink | FPGA関連 | FPGA | マスワークス | アルゴリズム | ハードウェア | アルテラ | ザイリンクス | 半導体設計(EDA) | シミュレータ | ASIC | メンター・グラフィックス

関連記事

最新ツールが支えるモデルベース設計

最新ツールが支えるモデルベース設計

組み込みシステムの大規模化、複雑化が進むに従って、ソフトウエア開発の負担が大きくなってきた。そこで数年前から注目されてきたのがモデルベース設計である。本稿では、モデルベースのソフトウエア開発をサポートするために、どのようなツールが開発されており、どのように活用されているのかを紹介する。- 「次世代エネルギーシステムにもMBDが有効」――MathWorksが「MATLAB/Simulink」の事業を拡大

- 「MATLAB/Simulink」の新バージョン、MATLABコードからCコードの生成が可能に

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.