シリコンパワーMOSFETの性能改善、素子構造よりもパッケージが効く時代に:パワー半導体(2/2 ページ)

鉛を全く使わない接合技術が役立つ

米Fairchild Semiconductorで低電圧MOSFET技術開発部門のバイスプレジデントを務めるクリス・レクサー(Chris Rexer)氏によると、「ウエハーの薄化によってオン抵抗を約25%低減でき、従来のワイヤボンディングからクリップへの移行によってさらに20%改善できる」という。さらに同氏は、「シリコンプロセスの世代を1つ進めるよりも、劇的な性能を改善できる」と続けた。

パワー半導体チップの接合に関連する効果的な技術は、クリップだけではない。拡散はんだ付け法(Diffusion solder)も、チップをパッケージにボンディングする際に重要になるだろう。拡散はんだ付け法は、ボンディング層が薄いことから、従来の手法と比べて低抵抗で、放熱特性も優れている。さらに鉛を含まない。RoHS指令などの「環境」への取り組みから考えても意義がある(図3)。

例えば、ELV指令(End of Life Vehicle directive)である。現在のELV指令はわずかな鉛の使用を限定的に認めているが、2014年に規定内容を見直すことが決まっている。そのとき、欧州車に使用するパッケージが鉛を全く含んではならないと要求してくる可能性もある。

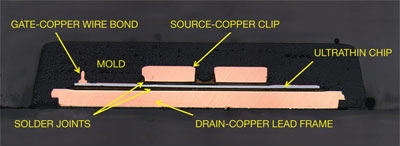

図3 SuperS08パッケージの断面図 Infineon TechnologiesのSuperS08パッケージである。トップサイドのマウント用クリップと拡散はんだ付け法の両方の技術を採用することで、パッケージの系全体で伝導損を削減している。MOSFETプロセス自体も薄ウエハー化を導入し、現時点でチップの厚さを60μmに抑えており、拡散はんだ付け法によって薄化したボンディング層がその特性を引き出すのに貢献している。

図3 SuperS08パッケージの断面図 Infineon TechnologiesのSuperS08パッケージである。トップサイドのマウント用クリップと拡散はんだ付け法の両方の技術を採用することで、パッケージの系全体で伝導損を削減している。MOSFETプロセス自体も薄ウエハー化を導入し、現時点でチップの厚さを60μmに抑えており、拡散はんだ付け法によって薄化したボンディング層がその特性を引き出すのに貢献している。Infineon Technologiesが発表した耐圧40VのパワーMOSFET「OptiMOS T2」は、薄化ウエハー技術と拡散はんだ付け法を組み合わせている。この手法について同社は、「現在のRoHS指令にある、シリコンチップをパッケージに接合するための鉛を含むはんだに関する規定水準を高いレベルでクリアしている」と主張する。

ハイ/ローサイドのMOSFETを単一パッケージにまとめる手法とは

電力密度が高まることでチップは小型化し、パッケージ技術が進歩した結果、ハイサイドとローサイドの2つのMOSFETチップを単一のパッケージにまとめるアプローチが現実味を帯びてきた。こうしたMOSFETドライバはこれまで、小型で低価格が要求される用途に向けるには、あまりにも大きく価格も高過ぎた。

しかし現在では、ローサイドとハイサイドそれぞれのMOSFETの特性を、設計によって容易に合わせ込むことができる。米Intelは2004年に初めて、このようなドライバの設計手法をDrMOS規格の中で提案した。しかし、コストが高くなることに加えて、設計が複雑になるため、当時は普及しなかった。現在では、パッケージの電力密度が増加したことで、そのようにペア化したMOSFETをまとめて封止した製品を実現できるようになっている。

米Texas InstrumentsのNexFET技術は、デバイス構造が縦型ではなく横型であることが特徴だ(図4)。横型構造を採用したことで、NexFET技術を採用した製品の耐圧は25Vに制限される。NexFET技術は、高い耐圧にも対応できるが、その場合、チップ面積が大きくなり、価格はかなり高くなるだろう。

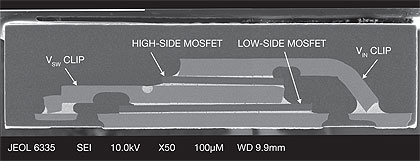

図4 PowerStack技術を利用したドライバチップの断面図 Texas InstrumentsのPowerStack技術を用いたPower Blockデバイスである。ハイサイドとローサイドのMOSFETは厚い銅クリップによって固定されていることが分かる。ローサイドのMOSFETチップは、リードフレームの本体部のパッドに接続され、電気的にグラウンドにつながる。このような構造により、小型で優れた電流レベルや電力効率、熱特性を実現している。

図4 PowerStack技術を利用したドライバチップの断面図 Texas InstrumentsのPowerStack技術を用いたPower Blockデバイスである。ハイサイドとローサイドのMOSFETは厚い銅クリップによって固定されていることが分かる。ローサイドのMOSFETチップは、リードフレームの本体部のパッドに接続され、電気的にグラウンドにつながる。このような構造により、小型で優れた電流レベルや電力効率、熱特性を実現している。NexFET製品は「PowerStack」と呼ばれる優れたパッケージ技術を取り入れている。同パッケージ技術を使用した製品は、単一パッケージの中にハイサイドとローサイドの両方のMOSFETを封止している。2つのMOSFETを水平に並べる構造に比べて、垂直に積層する構造は利点が大きい。回路の配線が短いために抵抗が低く、さらに重要なことにインダクタンスも小さくなる。同社によると、このインダクタンスの削減によって、800kHz〜1MHzというスイッチング周波数を実現できる。

†1 Conner, Margery, “GaN and SiC: on track for speed and efficiency,” EDN, Aug 25, 2011, pg 34..(待望の次世代パワー半導体:SiC/GaNデバイスは離陸間近)

†2 Clarke, Peter, “Infineon to make power ICs on 300mm wafers,” EE Times, Oct 12, 2011.(インフィニオン、300mm薄型ウエハーを使ったパワー半導体チップの初期生産に成功)

関連キーワード

MOSFET | ウェハ | シリコン | パワー半導体 | Infineon Technologies | はんだ | インダクタ | GaN | IGBT | フェアチャイルドセミコンダクター | RoHS指令 | SiC | Texas Instruments | トランジスタ | 電力効率

関連記事

SiC/GaNデバイスは離陸間近

SiC/GaNデバイスは離陸間近

待望の次世代パワー半導体 インフィニオン、300mm薄型ウエハーを使ったパワー半導体チップの初期生産に成功

インフィニオン、300mm薄型ウエハーを使ったパワー半導体チップの初期生産に成功

量産効果が高まる- 「実はプレステ3で300万個の量産実績」、ソニーがコアレスパッケージの進展明らかに

安定した品質を実現

Copyright © ITmedia, Inc. All Rights Reserved.