あらためて学ぶ、DDR2の高速化技術:高速シリアル・インターフェイス入門(2)(1/2 ページ)

今回取り上げる規格はDDR2です。パソコンのメインメモリとして広く利用されているDDR2はシリアル・インターフェイスではありませんが、信号の高速化のために共通した技術が用いられています。本稿ではこうした高速化技術を中心に解説をしたいと思います。

DDR2の概要

DDR2は、入手性や価格面で優位性があり、上記のようにパソコンのメインメモリとして用いられる以外にも、組み込み機器などで採用されています。その規格は、JEDEC Solid State Technology Association(JEDEC半導体技術協会)によってJESD79-2EとJESD208として規定され、公開されていますので誰でも入手することができます。

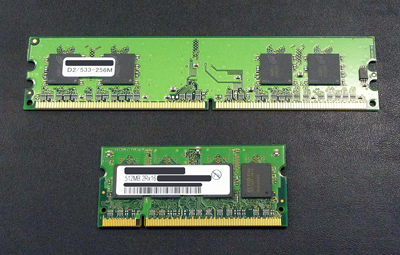

パソコン用のDDR2は、デスクトップ向け240ピン DIMM(Dual Inline Memory Module)(図1の上)と、ノートブック向け200ピン SO-DIMM(図1の下)に実装されています。組み込み機器の場合には、モジュールではなく直接実装する場合もあります。

DDRは、その名前のとおりクロックに対して2倍の速度となる高速データ・レート転送が可能であり、DDR2-400は200MHzのクロックでデータ・ライン当たり400Mbpsのデータ転送になります。JESD208で規定される最高速のDDR2-1066は、533MHzのクロックで1.066Gbpsの転送速度まで可能です。さらに高速のDDR3も規定されており、DDR3-2133で最高2.133Gbpsにまで達し、SATAのGen1 (1.5Gbps)よりも高速になっています。

高速化を支える技術

メモリ・モジュール単位で考えると、64ビット幅のパラレル・データ転送なので、純粋なシリアル・インターフェイスとは異なります。しかし、上記のようにDDR3では2Gbpsを超える高速データ転送が行われるために、克服しなければならない技術的課題には共通したものがあります。また、解決策もやはり同様の手法が使われています。本格的なシリアル・インターフェイスを考える前段階として、DDR2における特徴的な技術をいくつか取り上げたいと思います。

プリフェッチ

このプリフェッチは、DDRのデータ転送速度向上のための基本的な技術となっています。実は、DDR2の最高スピード・グレードのものは1Gbpsを超える高速データ転送を行いますが、内部のメモリ・コアそのものは、そこまで高速で動作するわけではありません。メモリ・コアの動作を速くするには、より大きな電力消費と高いコストが必要になりますので、内部のメモリ・コアの動作速度を低いままにインターフェイスの動作を高速に行う手法が取られています。

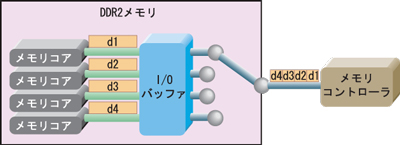

DDRでは、2ビット・プリフェッチと呼ばれる動作によりインターフェイスの動作を内部メモリ・コアの2倍の速度にしています。これは、I/Oバッファに別々のメモリ・コアから同時に2ビットのデータをあらかじめ読み出しておき(プリフェッチ)、この2ビットを順番に2倍の速度で送り出すというものです。2倍のデータ転送速度というのがDDR(Double Data Rate)の名前の由来となっています。DDR2は4ビット・プリフェッチと呼ばれる動作をし、バッファに4つのメモリ・コアからのデータを読み込みます。その結果、内部のメモリ・コアの動作速度の4倍の速度でデータ転送が行えます(図2参照)。

DDR3では、8ビット・プリフェッチが行われ、8倍の速度になるわけです。つまり、各データ・ラインにはパラレル/シリアル変換器が付けられてることになります。モジュール全体として見れば、64ビット・パラレル動作ですが、個々のデータ・ラインは高速シリアル・インターフェイスのように動作しているわけです。DDRで2倍のデータ転送速度を実現した際には、クロックの立ち上がりと立ち下がりの両方のエッジを基準にしてデータ転送を行っていました。

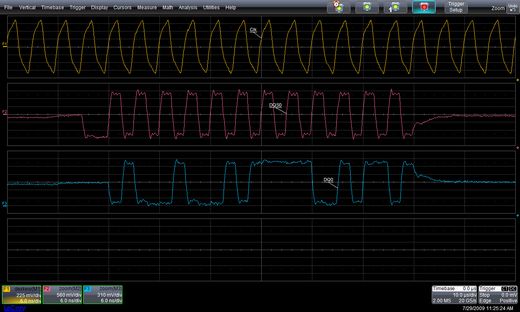

DDR2は内部のクロックの4倍の速度で動作していますが、外部クロックとデータの転送レートはDDRと同じ2倍の関係を維持しています。これは、内部のクロックが外部クロックの半分の周波数になっているということです。実際にインターフェイスの動作を制御するのはストローブ信号DQSの両エッジを基準に行われます。この信号のタイミングを図3に示しています。DQSの立ち上がりと立ち下がりの部分でデータが切り替わっていることが分かります。

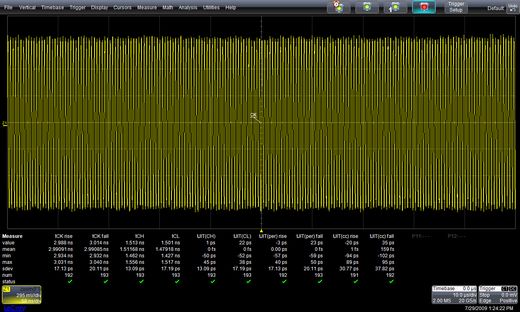

従来の同期回路の動作は、クロックの立ち上がり、または立ち下がりエッジでデータが切り替わるので、クロックの周期の変動をジッタとしてとらえることができました。しかしながらDDR2のクロックのジッタをとらえようとすると、立ち上がりと立ち下がりの両方のエッジを対象としなければならないので、JEDECではHalf Period Jitterという新しいパラメータを定義して半周期の変動を評価基準と定めています。

また677MHz以上のスピード・グレードにおいては、さらに新たなジッタのパラメータを追加して、より詳しいジッタの評価を行うことを規定しています。図5には、DDR2のクロックのジッタ評価をしている画面を示していますが、ここでは、立ち上がり時間、立ち下がり時間、ハイ側の半周期、ロー側の半周期、ハイ側の半周期のジッタ、ロー側の半周期のジッタ、立ち上がりエッジで計測した周期のジッタ、立ち下がりエッジで計測した周期のジッタ、立ち上がりエッジで計測したサイクル・サイクル・ジッタ、立ち下がりエッジで計測したサイクル・サイクル・ジッタの10項目が同時に計測されています。しかし実際には、クロック・ジッタの評価項目は約100項目もあるので、何度もパラメータを切り替えながら評価しなければなりません。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 DDR2メモリ・モジュール

図1 DDR2メモリ・モジュール 図2 DDR2メモリの内部構造

図2 DDR2メモリの内部構造