複雑なA/Dコンバータの回路構成を極める!:いまさら聞けないコンバータ入門(2)(1/3 ページ)

民生機器、計測、通信、自動車、工業機器、医療器など、さまざまな分野に使われて「データ・コンバータ」。今回はA/Dコンバータについて解説する。

前回はメジャーなコンバータ素子回路の特長、そしてその使い方の基本として、D/Aコンバータを紹介しました。今回はA/Dコンバータについて解説します。

A/Dコンバータの基本構成とその特長

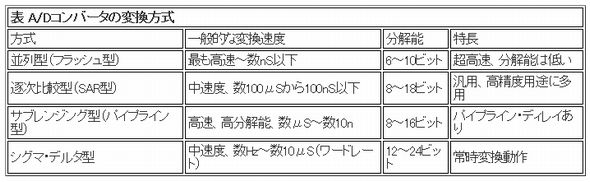

アナログ入力信号をデジタル出力信号に変換するA/Dコンバータには、D/Aコンバータよりも多くの回路構成があります。現在広く使われている方式は、以下の表にあるものです。

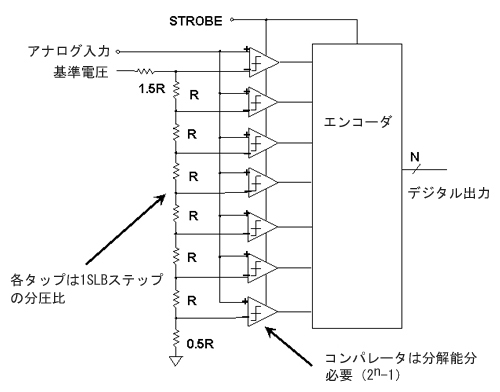

前回、多くのA/Dコンバータは、内部に比較用のD/Aコンバータを内蔵していると述べましたが、フラッシュ・コンバータと呼ばれる並列型A/Dコンバータは、そこにデジタルポテンショメータ型の素子を使用しています。この抵抗のタップの電圧と入力されたアナログ信号の電圧を、高速アナログ・コンパレータで比較し、その位置をデコードしてデジタル値に変換します。

従って、変換速度は、ほとんどこのコンパレータの反応速度により決まります。A/Dコンバータの構成としては、最も高速の動作が期待できる(低い分解能ではGHz帯域の変換が可能)ので、デジタル・ストレージ・スコープなどに使用されていますが、最近では後に述べるサブレンジング型やシグマ・デルタ型A/Dコンバータ内部のビルディング・ブロックとして使われることの方が多いようです。

この方式の弱点は、分解能の数だけコンパレータが必要で、その規模が非常に大きくなってしまうことです。例えば10ビットの場合、1024個のコンパレータが並列に接続され、入力信号はこれらを低ゆがみで駆動するために、その駆動アンプにかなり強力なものを必要とします。また抵抗ストリングの精度や、コンパレータの精度によるリニアリティエラーがあるため、いまのところ10ビット程度がその限界です。

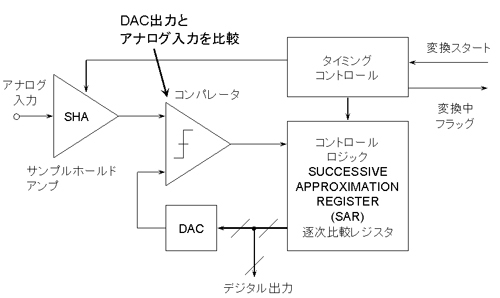

並列型は比較を一遍に行いましたが、これをD/Aコンバータの1ビットごとにシリアルに行うようにしたものが、逐次比較型(Successive Approximation Register 略してSAR)A/Dコンバータです(図2を参照してください)。

比較はSARというシーケンサによりシリアルに行われるため、コンパレータは1つで済みます。比較は内蔵D/Aコンバータのビット数だけ行われます。変換のアルゴリズムは15世紀から知られている方法で、てんびんで未知の重さを最小の計測回数で量る方法を応用したものです。

図2をご覧ください。1、2、4、8……という重みを持ったD/Aコンバータの各ビット出力と入力信号を比較して、各ビットのオン・オフを決めていきます。最終的にはD/Aコンバータのコードが、変換データとなります。

このD/Aコンバータ部分は、最近では抵抗ラダーではなくコンデンサ・ラダーによるものが増えてきています。このコンバータは、ビットを順番に比較していくため、そのシーケンスの最中に入力信号が1LSB以上動いてしまうと(D/Cや極低周波では問題ない)、その結果が不正確になります。

そのため、入力信号の動きを変換中だけ一時止める、サンプル・ホールド・アンプあるいはトラック・ホールド・アンプがほとんどの場合必要です。最新のデバイスは、この回路をチップ上に集積していて、サンプリングA/Dコンバータと呼ばれることもあります。

逐次比較型A/Dコンバータは、扱いやすい回路規模と比較的低ノイズで、現在汎用から高精度コンバータの分野で最も広く使われています。8ビットから18ビットという高精度のものまで、モノリシックICとして供給されています。変換速度はビット数にもよりますが、数10K SPS(Kilo Samples Per Second)から数10MSPS(Mega Samples Per Second)くらいまでです。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 並列型(フラッシュ型)A/Dコンバータ

図1 並列型(フラッシュ型)A/Dコンバータ 図2 逐次比較型(SAR型)A/Dコンバータ

図2 逐次比較型(SAR型)A/Dコンバータ 図3 逐次比較A/D変換のアルゴリズム

図3 逐次比較A/D変換のアルゴリズム