DSP選定に役立つLSIの分類とDSP、ASICの比較:イチから学ぶDSP基礎の基礎(7)(1/2 ページ)

今回は、DSPとASICの違いについて解説します。

ユーザー側の立場から見たASICの特徴は、(すでにDSPとの比較を行った)FPGAと同じとみてよいでしょう。一般的に、DSPは比較的サンプリング周波数は低いが複雑な処理を行うのに適しているのに対し、ASICはサンプリング周波数は高いけれども比較的演算量が少ない処理、あるいは多チャネルを並列処理するようなシステムに向いています。

ここではデジタル信号処理の話からは少し離れて、LSI設計・製造の面から標準品であるDSPとユーザーが回路設計をするASICとを比較してみたいと思います。現在はASICの小ゲート・低価格製品はFPGAに押されて退潮し、数千万円単位の開発費が掛かる大規模製品が主流となっています。もはやASICは誰でも気軽に使えるような製品ではありませんが、ASICとの比較で標準品であるDSPの特徴を知ることは有益だと思います。

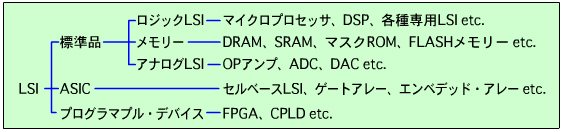

LSIの種類を大まかに分類すると表1のようになります。表1はLSIの機能・用途による分類ですが、それだけではなく製造プロセス、デバイス構造や設計手法の違いが存在します。

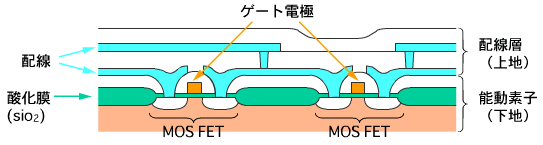

初めに、デバイス構造の違いから見ていきましょう。大まかにいって、LSIは能動素子部分とその上部の配線層から構成されています。以下ではそれぞれを下地、上地と呼ぶことにします。

アナログLSIに用いる能動素子はバイポーラ・トランジスタが主流ですが、それ以外のLSIはMOS FETを用いています。MOSデバイスの中でもメモリ製品の多くは下地に特殊な構造を有しています。例えば、DRAMにはデータ保持用のコンデンサが、FLASHメモリには同じくデータ保持用のフローティング・ゲートがあります。

では、DSPをはじめとするロジックLSIの標準品と、セルベースLSI、ゲートアレイなどのASICとの間にはどのような構造的な相違があるのでしょうか? 実はこれらのロジック系のLSIは構造は同一です。CMOS FETからなる下地と多層配線層(上地)から構成されています。

標準品とASICを両方手掛けているLSIメーカーでは、かつてはそれぞれに異なる製造プロセスを用いていたことがありました。プロセッサは集積度を重視した製造プロセス、ASICはスピードを重視したプロセスを用いていたのです。しかし、LSIの微細化/高速化の進展によってそれぞれを異なる製造プロセスで作り分ける必然性が消滅し、現在では標準品のロジックLSI(DSPなど)とASICの製造プロセスの統合化が進んでいます。

次にDSPとASICの違いをLSIとしての設計ツール、設計手法の面から見てみます。実は設計ツールに関しても、DSPとASICに大きな違いはありません。どちらも回路シミュレーションや論理合成、レイアウトには大手EDAベンダ製の市販ツールをチップ設計に用いています(一部の日本メーカーは内製ツールをASICユーザーに提供しています)。

設計手法の面では、現在はDSPやマイクロプロセッサなどの標準品もASICと同様に設計の自動化が進んでいます。LSIの集積度が低かったころのように、標準品で細かいファンクション・ブロックのレベルからすべてを人手でレイアウト設計するようなことはありません。

現在ではあらかじめ製品ファミリーに共通のIP(例えばALU、乗算器、メモリなど)を社内専用のライブラリとして用意しておき、個別製品の設計時にはIPと論理合成・自動配置配線ツールを用いて作ったランダム・ロジックを組み合わせて使うという手法が一般的です。

Copyright © ITmedia, Inc. All Rights Reserved.

表1 LSIの分類

表1 LSIの分類 図1 MOS LSIの構造の概略(断面図) この分類はあくまでも一例です。FPGA、CPLDなどはASICの中に含めずにプログラマブル・デバイスとして独立して扱っています

図1 MOS LSIの構造の概略(断面図) この分類はあくまでも一例です。FPGA、CPLDなどはASICの中に含めずにプログラマブル・デバイスとして独立して扱っています