ブラックボックスのFPGA、基板の回路設計に潜むわな:Wired, Weird(3/3 ページ)

FPGAと周辺パターンが発振器に

次に紹介するのは、FPGAを含む一部の回路のアナログ的な振る舞いが基板の不良につながったという事例である。基板のパターン設計が絡んだ、極めて難解な不具合だった。不良の発生頻度が非常に低く、再現させるのも苦労した。

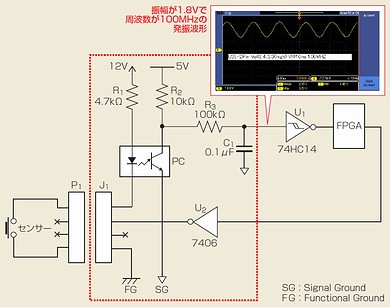

問題の回路図の概略を図3に示す。センサーの作動を通知する信号を受け取り、フォトカプラ(図中のPC)を介して絶縁バリアをまたいだ上で、CRタイマー回路(コンデンサC1と抵抗R3)とシュミットトリガー入力の論理インバータIC(図中のU1で品種は74HC14。以下、INVと略す)を経由してから、FPGAの入力端子に信号を印加するという構成だ。

図3 不具合が起きた基板のFPGA周辺回路 黄色い点線で囲んだ部分はコネクタ(J1)のすぐ近くに配置されているが、論理インバータIC(U1)とFPGAはそこから20cm程度も離れた位置に実装されていた。 (クリックで画像を拡大)

図3 不具合が起きた基板のFPGA周辺回路 黄色い点線で囲んだ部分はコネクタ(J1)のすぐ近くに配置されているが、論理インバータIC(U1)とFPGAはそこから20cm程度も離れた位置に実装されていた。 (クリックで画像を拡大)図3の動作を簡単に説明しよう。センサーと基板はコネクタを介して接続されている。センサーがオンすると基板に信号が伝わって、フォトカプラの1次側にあるLEDに約2mAの電流が流れ、2次側のフォトトランジスタ出力がオンになる。そのオン信号は、CRタイマー経由でINVを通過することで、遅延が約10ms加わって論理レベルが反転した状態でFPGAに入力される。また、これは当初は認識しておらず後で分かったことだが、FPGAからコネクタへと、フィードバック用の信号が出力されていた。

不具合基板が筆者の手元に届いたので、回路の動作を詳細に確認した。センサーの信号をオフにして、オシロスコープのプローブでINVの入力端子を当たると、2.5Vを中心に約1.8Vの振幅で周波数が100MHz程度の連続発振波形が見えた。

前述の通り、INVはシュミットトリガー入力の論理インバータである。そのヒステリシス(論理レベルのHi/Lowを判断する2つのしきい値電圧の幅)に相当する約0.8Vを超えた発振が起こっていた。しかも100MHzと高い周波数での発振現象である。さらに調べると、電源の5V電圧やグラウンド電位も大きく変動していた。しかしオシロスコープのプローブをINVの出力端子に移すと、この発振は停止した。

原因究明のため、基板に実装された部品の位置を確認した。この基板は面積が30×10cm程度の細長い形状である。図3の点線で囲んだ部品はコネクタのすぐそばに配置されており、INVとFPGAはそれらから20cm程離れた場所に実装されていた。

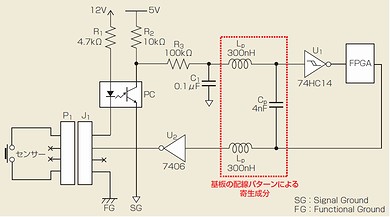

FPGAへの入力と出力の2本の配線パターンを追いかけてみたら、大変なことが分かった。INVの入力端子に至る配線とFPGAから出力されたフィードバック信号の配線が、20cmもの長距離にわたって0.3mmと狭い間隔で並行して引きまわされていた。電気的に見れば、長い配線パターンはインダクタンス成分として、近接した2本の長い配線パターンは容量成分としてそれぞれ機能する。これを等価回路として図3に追加したのが図4である。

図4 電気的影響が大きい配線パターンを等価回路で追加 図3に、基板の配線パターンを等価回路として追加した。黄色い点線で囲んだ2個のインダクタと1個のコンデンサがその等価回路である。FPGAの入力と出力がこのコンデンサ(容量成分)を介して結合し、負帰還がかかった形になっている。 (クリックで画像を拡大)

図4 電気的影響が大きい配線パターンを等価回路で追加 図3に、基板の配線パターンを等価回路として追加した。黄色い点線で囲んだ2個のインダクタと1個のコンデンサがその等価回路である。FPGAの入力と出力がこのコンデンサ(容量成分)を介して結合し、負帰還がかかった形になっている。 (クリックで画像を拡大)この図中、容量成分を示すCPに注目してほしい。FPGAの出力からINVの入力へと、このCPを介して負帰還の信号が流れ込んでいる。発振の原因はここにあった。

確認のため配線パターンを一部カットしてジャンパー線でつないだら、発振が止まった。また上述のように、オシロスコープのプローブをINVの出力端子に当てても発振は止まった。これはプローブを接続することで10pF程度の容量成分が追加された形になり、遅延時間が発生することで発振が停止するものだと考えられる。こうして、基板上の帰還をなくすか、FPGAの入力と出力の間に時間遅れを作ることで発振が止まることが分かった。

FPGAならではの方法で対策

原因が判明し、設計変更の方法をいろいろ検討した。基板のパターンを変更すると現場での基板の交換作業が発生し、対策費用が大きくなる。FPGAのプログラム変更で対策できれば、基板はそのままに現場でプログラムを書き換えればよく、最小コストで対策を施せる。

そこでFPGAのプログラムを修正し、INVから受け取った信号をフィードバック用に再出力する前に遅延させる回路をFPGA内部に追加してみた。基板の動作を確認したところ、見事に発振が止まったので、この方法を採用して動作不良の対策を実施した。これは、FPGAを実装した基板ならではの方法だといえる。

FPGAは、基板の回路図では通常、ブラックボックスとして表現されている。内部のプログラムは、回路図を見ただけでは分からない。だが、それを把握しなければ、出力の条件は理解できないのである。そのため、不具合動作が分かりにくく、再現性も低いのでなかなか原因を見つけにくい。

その一方で、FPGAを設計する上での禁止事項や、FPGAのハードウェアの特性がまだ十分に理解されていない部分もあり、それが落とし穴となって、それに起因した“隠れた不具合”が基板に残ってしまう可能性がある。FPGAを用いる基板に向けて、そうした不具合を事前にあぶり出せるように、設計検証の手法を標準化する必要があるだろう。

《次の記事を読む》

関連キーワード

FPGA | アイソレータ | 計測機器 | オシロスコープ | ザイリンクス | Wired, Weird | CPLD | インダクタ | 発振器 | PLD | プログラマブルロジック(エレクトロニクス) | ルネサス エレクトロニクス

Copyright © ITmedia, Inc. All Rights Reserved.