ハイサイド・ドライバーでIGBTを駆動:Design Ideas パワー関連と電源

低電力/中電力の電源システムに向けたパルス幅変調(PWM)器とハイサイド・スイッチのインターフェース回路を紹介する。FETを2つ使えば、大電力用途に対応することも可能だ。

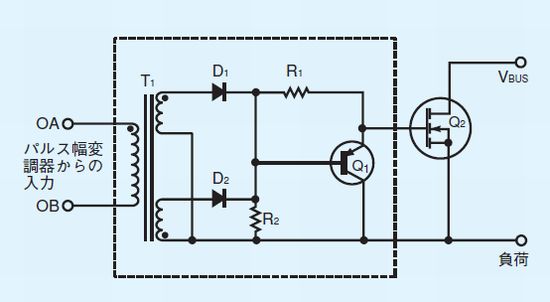

図1は、低電力/中電力の電源システムに向けたパルス幅変調(PWM)器とハイサイド・スイッチのインターフェース回路である。ハイサイド・スイッチにはIGBT(insulate gate bipolar transistor)、もしくはMOSFETを使える。ICL7667やMIC4423のようなFETドライバーをバッファとして使用すれば、この回路をTTL/CMOS回路とHブリッジ回路のインターフェースに使うことも可能である。

この回路の入力部であるOAの電位が上がると、D1が導通状態になる。その結果、電流がR1を介して流れ、FETのゲート容量が充電される。FETのターンオン時間は、R1の値と駆動信号に対する出力インピーダンスで決まる。FETのゲート容量が充電されると、R1の両端の電圧はほとんど0Vになり、Q1はオフ状態になる。その後パルス幅変調器がデッドタイムに入ると、ゲート容量に充電された電荷がQ1とR2を通して放電される。FETのターンオフ時間は、R2とQ1のhFEで決まる。この回路を使えば、150ns以下のターンオン/ターンオフ時間を実現できる。

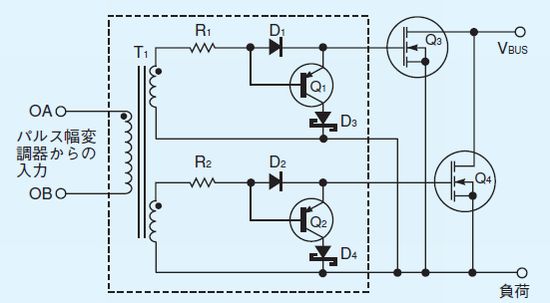

大きな電力を必要とする電源システムには、FETを2つ使うことで対応できる(図2)。このターンオン時間を決めるのは、R1とR2の値と、パルス幅変調器もしくはFETドライバーの出力インピーダンスである。一方、ターンオフ時間は、R1とR2の値と、Q1とQ2のhFEの値で決まる。ショットキー・バリアー・ダイオードであるD3とD4は、駆動信号が負の場合に、Q1とQ2のコレクター‐ベース接合部を介して電流が流れることを防止する。この回路で得られるターンオン時間とターンオフ時間は、トランスの出力インピーダンスに依存するが、それぞれ50ns以下、100ns以下である。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 低コストで実現できるハイサイド・スイッチ駆動回路

図1 低コストで実現できるハイサイド・スイッチ駆動回路 図2 並列に接続した2つのFETで大電力用途に対応

図2 並列に接続した2つのFETで大電力用途に対応