FPGAにステートマシンを実装する、アーキテクチャと実装手法の選択が要諦:プログラマブルロジック FPGA(1/2 ページ)

FPGAに搭載するカスタム回路は、状態マシン(ステートマシン)を基盤にして開発するケースが少なくない。そのステートマシンを実装する際に、正しいアーキテクチャと適切な実装手法を選択すれば、最適なソリューションを実現できる。

FPGAの用途の1つに、簡単な通信プロトコルを実行するといったシーケンス制御がある。シーケンス制御の実装には、状態マシン(ステートマシン)を活用する手法が最適だ。

ステートマシンとは、有限な数の状態(ステート)の間を行き来するタイプの論理回路で、同時に複数の状態を取ることはできず、任意の時点で必ずある1つの状態を取る。そしてトリガー信号を受けると、ある状態から別の状態に遷移する。

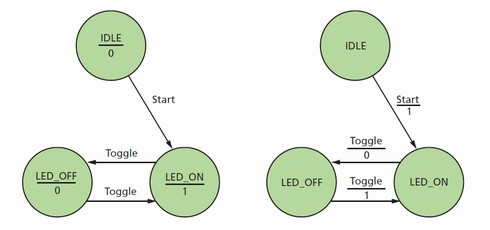

ステートマシンには、ムーア(Moore)型とミーリー(Mealy)型がある。ムーア型(ムーアマシン)の出力は、現在のステートによってのみ決まる。代表的なムーアマシンとしては、カウンタが挙げられる。一方、ミーリー型(ミーリーマシン)の出力は、現在のステートと入力の値によって決まる。代表例にはリチャードコントローラがある。

ステートマシンを記述する

ステートマシンを記述する最初の作業は、状態遷移図の作成である。状態遷移図では、「各ステート」と「状態間の遷移」、「ステートマシンからの出力」を記述する。例えば図1は、LED(発光ダイオード)をオン/オフするステートマシンを記述した状態遷移図である。この図で左側にある遷移図はムーアマシン、右側にある遷移図はミーリーマシンで定義したものだ。

FPGAが登場する以前は、こうした状態遷移図の実装にはそれなりの手間がかかっていた。現在のステートテーブルと次のステートテーブルを生成し、ステートマシンの実装に必要な論理回路を作成しなければならなかった。FPGAを使えば、状態遷移図を直接、FPGAに実装できる。

VHDLと相性の良いASMチャート

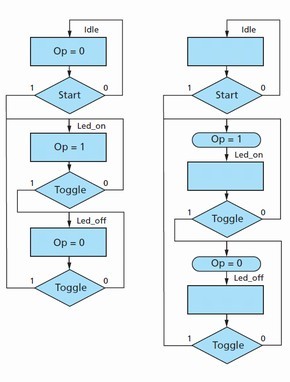

ステートマシンの多くは図1のような状態遷移図で記述されているが、ステートマシンを記述する手法は他にもある。例えば、ASM(アルゴリズミックステートマシン)チャートである。ASMチャートは、ソフトウェア開発におけるフローチャートと似たチャートでステートマシンを記述する。図2のASMチャートは、図1の状態遷移図を記述し直したものである。左側がムーアマシン、右側がミーリーマシンになっている。

ASMチャートは次の3つの基本要素で構成されている。

- 状態ボックス:ステート名が付与され、ステート出力のリストを含む(ムーアマシン)

- 決定ボックス:条件が「真」であるかどうかを検証し、次のステートに進むかどうかを決定する

- 条件付き出力ボックス:現在のステートと入力によってミーリー出力を記述できるようにする

状態遷移図と違い、ASMチャートはVHDLなどのハードウェア記述言語で実装しやすい。従って、FPGA開発者の得意分野によってはASMチャートの方が使いやすいだろう。

ムーアマシンか、ミーリーマシンか

ムーアマシンとミーリーマシンのどちらを選択するか。これは、ステートマシンが特定の時間内に実行しなければならない機能によって決まる。2つのマシンの主な違いは、入力に対する応答にある。

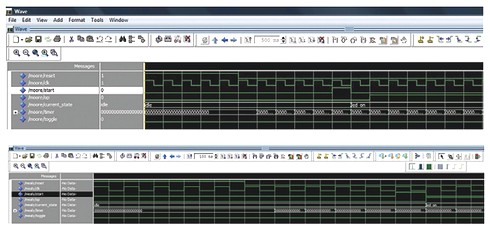

ムーアマシンは、入力と出力セットの間に短くとも1クロックサイクルの遅延が生じる。従ってムーアマシンでは、入力の変化に対して即座に応答することができない(図3)。これに対してミーリーマシンは入力に対して即座に応答するので、同じ機能を実現するために必要な状態数は、通常はムーアマシンよりもミーリーマシンの方が少なくて済む。

ミーリーマシンの問題点は、他のステートマシンと通信するときに、競合状態が発生する恐れがあることだ。この競合状態は、他のイベントのタイミングあるいはシーケンスに依存しており、予期しないタイミングで、しかも必ず発生する。

実装するステートマシンをムーアマシンとミーリーマシンのどちらかに絞る必要はない。両方のマシンを適切に選択することで効率を高めた、ハイブリッド型のステートマシンを作成することが可能である。例えばRS-232シリアルデータを受信するステートマシンは、ハイブリッド型で実現できる。

ステートマシンの実装

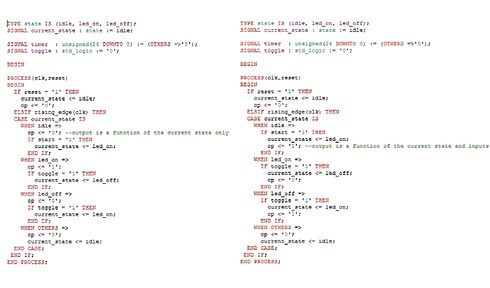

VHDLを使用すると、ASMチャートからステートマシンを直接に、しかも簡単に記述できる。VHDLは列挙型変数をサポートしているので、実際の状態名を定義できる。例えば次のような型宣言文を考えよう。

TYPE state IS (idle, led_on, led_off) ;

この型宣言文は、ボタンを押すたびにLEDの点灯(オン)と消灯(オフ)を切り替えるステートマシンの状態遷移図(図1)に対応する。

ステートマシンの実装にはいろいろなやり方があるが、基本的な手法は、次の2つに分類できる。1つは、ワンショットアプローチである。単一のプロセスにすべての処理を組み込む手法だ。もう1つは、2プロセスアプローチである。回路を組み合わせ論理と順序論理に分けて扱う。

一般的には、単一のプロセスでステートマシンを実現するワンショットアプローチの方が、エンジニアには好まれる。2プロセスアプローチに比べて、以下のような利点があるとされているからだ。

- ラッチを生成する組み合わせ論理で、信号のカバーが十分でなくなるリスクを取り除ける

- ステートマシンの出力タイミングがクロックに同期している

- 2プロセスアプローチに比べるとデバッグが簡単なことが多い

どちらの手法を選択してステートマシンを実装したとしても、図4に示すように、CASE文を使用して、次の状態の決定と出力を評価することになる。なお図4は、単一プロセスアプローチでムーアマシン(左側)とミーリーマシン(右側)をVHDL記述したものである。

Copyright © ITmedia, Inc. All Rights Reserved.