解析実行エラーの原因と対策(その3):SPICEの仕組みとその活用設計(8)(2/3 ページ)

理想化素子の振る舞い

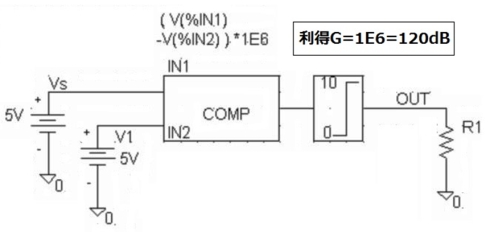

図2は具体的なICの要求特性を決めるための事前検討に理想化コンパレータとして、数式モデルを使ったものです。

しかし、このコンパレータをヒステリシス型の発振回路に使用すると、発振動作をしなかったり、途中で停止してしまったりすることがあります。これは、ゲインが100万倍とはいえ、有限なため入出力のバランスの取れる点が必ず存在し、その状態で回路が安定化されるからです。

図2の例であれば、入力間に5μVの差分を生じた時に出力が5Vになるので、正帰還をかけても安定してしまうからです。

実際の回路では、ノイズや動作の時間的遅れがあり、このような安定状態になることはあり得ません。しかし、SPICE上では電圧分解能が1μVですので安定状態に成り得るのです。

対策

これは理想化が過ぎた例と言えるでしょう。対策としては、実回路と同じように、若干の時間遅れ要素を経由して正帰還を行い、オーバーシュートを発生させます。このように実際に近づけてやることで、時間的な安定点をなくして回路を発振させることができます。

DC解析エラーの例

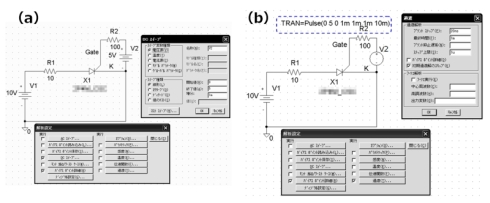

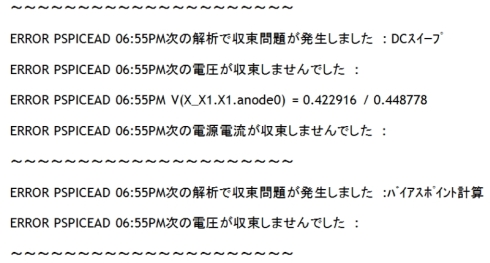

図3は、サイリスタのターンオン電圧の感度を調べるため、ゲート電圧V2をパラメータとしてDCスイープ解析を実行した場合に、ITL2=20の制限で解析が打ち切られ、解析が途中で停止した例です。

対策

DCスイープ解析ではなく図3(b)のようにゲート信号V2を傾斜を持つ電圧源として過渡解析を実行すると失敗しにくくなります。これは、DCスイープ解析が条件変更の都度、回路全体の安定点を求めるのに対して、過渡解析は前回の解析結果(安定値)を前提にして解を求めているので状態の変化幅が狭く、収束しやすいことによります。

図3(b)ではゲート信号を可変していますが、この手法は電源自体を緩やかに立ち上げたり、回路の各部が安定してから信号を遅れて立ち上げるなど、広く応用することができますので覚えておいてください。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 理想化コンパレータ

図2 理想化コンパレータ

図3(a)のDCスイープ解析でのエラーメッセージ(原メッセージは英文ですが、翻訳してあります)

図3(a)のDCスイープ解析でのエラーメッセージ(原メッセージは英文ですが、翻訳してあります)