PLL(Phase Locked Loop:位相同期ループ):これだけは知っておきたいアナログ用語

PLL(Phase Locked Loop:位相同期ループ)

PLLとは、Phase Locked Loopの略で、日本語では位相同期ループと呼ぶ。入力信号の位相と、出力信号の位相を一致させる、すなわち同期を取る役割を果たすアナログ回路である。基本的なアナログ回路ブロックの1つである。

PLL単体でIC化されて市場に投入されている他、無線通信用トランシーバICや、周波数シンセサイザIC、クロック・ジェネレータIC、クロック・ジッタ・クリーナICなどにも集積されている。

ネガティブ・フィードバック回路で構成

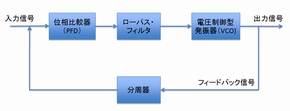

図1 PLLの基本回路構成

図1 PLLの基本回路構成位相比較器(PFD)、ローパス・フィルタ、電圧制御型発振器(VCO)、分周器などの回路ブロックから構成される。ネガティブ・フィードバック回路を構成することで、入力信号と出力信号の位相の同期を確保する

PLLは、位相比較器(PFD:Phase Frequency Detector)、ローパス・フィルタ、電圧制御型発振器(VCO:Voltage Controlled Oscillator)、分周器などの回路ブロックを使い、ネガティブ・フィードバック(負帰還)回路を構成することで実現する(図1)。例えば、入力信号と、フィードバックされた出力信号の位相が同期していない場合、位相比較器においてそれが検出され、誤差信号パルスが出力される。このパルス信号は、ローパス・フィルタを通過することで直流(DC)電圧に変換される。VCOにこの直流電圧が入力されると、その値に応じて、その出力信号の周波数が変化する。こうすることで、入力信号と出力信号の位相を同期させるわけだ。

VCO出力のフィードバック・ループに分周器を入れると、入力信号の周波数を任意の整数倍に高める機能を付加することができる。こうした回路をPLL周波数シンセサイザと呼ぶ。

なお、PLLには、「デジタルPLL」と呼ぶ回路方式が存在する。これは、位相比較器と分周器をデジタル回路で構成したものだ。ローパス・フィルタやVCOは、アナログ回路で構成している。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2015年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード