サイプレスの65nm非同期SRAMでSingle Event Upset(SEU)を軽減:軽視していませんか? メモリの放射線対策

[Nilesh Badodekar, サイプレス セミコンダクタ]

はじめに

システム設計者にとって、メモリ デバイスの信頼性とデータ インテグリティは最も重要な関心事の2つである。昨今のシステムは、放射線などの環境ファクターによるメモリ内のデータ破損に対する耐性が弱い。そのため、信頼性の高いメモリ デバイスを使用することが重要課題となっている。システム設計者は、高信頼性を得るためにオフチップで誤り訂正や冗長性を持たせる技術に頼らざるを得ない。だが、これら技術は、プリント基板のスペースをとったり処理に追加で時間がかかったりするため、オーバーヘッドの要因となる。サイプレスの最新世代SRAMは、シングルチップに誤り訂正符号(ECC)を搭載しており、ボード スペースやコストを抑えるだけでなく、デザインの複雑性も軽減する。これら製品は、ECCを搭載していないSRAMでFITレートが150FIT/Mビット以上になるところを、0.1FIT/Mビット以下に抑えるという高信頼性を実現している。また、SRAM内の誤り訂正をモニタリングする機能を新しく提供している。本記事では、その新機能を含め、サイプレスSRAM製品が提供するSEU軽減技術を解説する。

Single Event Upset(SEU)

Single Event Effect(SEE)は、デバイスが動作する環境で発生する荷電粒子(α粒子や高エネルギー中性子、熱中性子)によってデバイス内の論理状態を変えてしまったり過渡電流を発生させてしまったりすることをいう。半導体デバイス内に高エネルギー中性子が侵入すると、「ソフトエラー」と呼ばれるデータの反転を引き起こしたり、「ハードエラー」と呼ばれる定常的なダメージが発生したりする。ソフトエラーでは、デバイスをリセットまたはリライトすることにより通常の状態に回復させることが可能なため、破壊の原因にはならない。一方、ハードエラーは、デバイスを破壊してしまう。ハードエラーの一般的なものとして、Single Event Latch-up(SEL)や高電流もしくは熱暴走によって起こる後続損害が挙げられる。

1個の放射線粒子が入射することで起こるソフトエラーはSingle Event Upset(SEU)と呼ばれる。SEUはSingle-bit Upset(SBU)またはMultiple-bit Upset(MBU)で表されます。SBUは、1個のエネルギー粒子が衝突することによって1ビットが反転することをいう。MBUは、1個または2個以上の放射線粒子が通過することにより複数ビットが反転することを指す。

プロセス テクノロジの細分化(90nmから65nmまたはそれ以下)により、メモリのセル サイズはどんどん小さくなっている。これにより、コア電圧もより小さくなっている(1.8Vから1.2Vまたはそれ以下)。そのためメモリセル内の静電容量が縮小され、結果として、アップセットを引き起こす要因となるクリティカル チャージ(セル内にデータを保持するために最低限必要とされる電圧)が低下し、よりSEUを引き起こしやすくなる。低エネルギーのα粒子や宇宙線でさえセルには支障となってきています。

SEUはランダムで、デバイスにダメージを与えないので壊滅的なものではない。多くの民生システムは、一定のレベルまでのソフトエラーへの耐性を持っている。しかしながら、ミッション クリティカルなアプリケーションにおいては、ソフトエラーはデータの破損だけでなくシステムそのものの破壊につながる重大なインパクトを与える可能性がある。

SEUの軽減

非同期SRAMにおけるソフトエラー軽減の主要な技法は、プロセス テクノロジ レベルまたはシステム レベル、チップのデザインやアーキテクチャを変更することである。だがこの技法を用いるには、プロセス技術が必須で、セル レイアウトの変更に高額な費用が発生したり、デバイス性能にネガティブなインパクトを与えたりする可能性がある。システムレベルの軽減においては、SRAMを複数使用したりソフトウェアにECCスキームをインプリメントしたりすることで対応が可能だが、この方法はボードスペースや実行時間にオーバーヘッドを起こしてしまう。また、ボードやソフトウェアに追加のデザインが発生するため、デザインの複雑性が増す。一方、チップ アーキテクチャレベルの変更は、透過的でソフトエラー軽減の有効的な手段である。

チップデザインおよびアーキテクチャの変更

誤り訂正コード(ECC)やビット インターリービングの統合などのアーキテクチャ レベルの拡張により半導体デバイスのソフトエラーを低減することができる。

ECCの組み込み:ソフトウェアに実施された誤り訂正や符号化は、チップ アーキテクチャのハードウェア レベルにて実現しており、訂正はシステム設計者へ明白となる。

ビット インターリービング:高エネルギー粒子が半導体の原子と衝突すると、複数のセルに影響を及ぼす。1個のエネルギー粒子が1ワード内の2ビットまたはそれ以上に影響すると、MBUが発生する。SRAMアーキテクチャにビット インターリービング テクニックを組み込むことで、このMBUの回避に役立つ。ビット インターリービングは物理的に隣接するビット ラインを異なるワード レジスタにマップする。ビット インターリーブは、連続する2ビットを同一ワード レジスタ内に別々にマップする。ビット インターリーブの距離が複数のセル ヒットに拡散した場合、1ワード内でのMBUではなく、複数ワード内でのSBUとなる。ビット インターリーブされたメモリ内では、シングルビット誤り訂正符号の訂正アルゴリズムがすべてのエラーを検出および訂正に使用される。

サイプレスの65nm非同期SRAMでのソフトエラー軽減

サイプレスの65nm SRAMは、シングルビットのソフトエラー軽減にハミング コードを使用する。ハミング コードはECCスキームとして良く知られている信頼性の高いものである。ここからは、サイプレスSRAM製品で使用されているハミング コードについて解説する。

ハミング コード

ハミング コードは、(7,4)ハミング コードで一般的に使用される線型の誤り訂正符号の1つである。次の等式は、符号長nのハミング コードを表すベーシックなものである。

一般的には、

k=データ ビット数、m=パリティ チェック ビット数、n=符号長で構成され、n=m+kで表される。

サイプレスSRAMのメモリ アレイは32ビットのワード スペースで構成されている。32ビットのデータ ワードの場合、mの最も小さい値は6である。この場合、符号長(n)は38となる。ゆえに、サイプレスのシングル ビット エラーの検出および訂正には、(32,38)ハミング コードが使用されていることになる。

サイプレスのECC付きSRAM

サイプレスの65nm非同期SRAMは、ハードウェアとしてECCブロックを搭載しており、すべてのECC関連機能がインラインで動作する。この場合、エンコードはユーザーの介入無しで、デバイスのアクセス時間性能に影響することなく動作する。

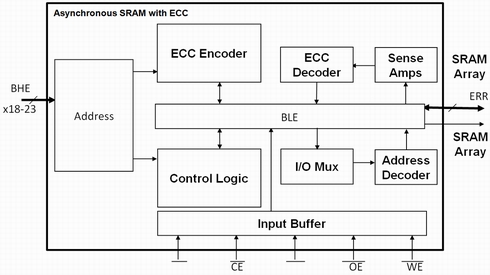

シングルビット エラーの検出および訂正は、16ビット インターリービング スキームごとに動作することでマルチビット エラーの発生を回避する。図1は、サイプレスの65nm非同期SRAMの内部構造を示す。

メモリへの書き込み動作ごとに、32ビット データにつき6個のパリティ ビットが格納される。サイプレスのSRAM製品はオプションで「ERR」と呼ばれる出力ピンを提供しているが、このERRピン(ERRピン付きのデバイスには専用の部品番号を付与)は、読み込み動作中にエラー検出および訂正が行われると、そのシングルビット エラーごとにフラグを立てる。

サイプレスの65nm SRAMは(32,38)ハミング アーキテクチャを採用しているため、読み込み動作ごとにシングルビット エラーを検出および訂正することが可能である。ERRピン搭載のデバイスではさらに、それら検出および訂正が行われる度に、ロジックのHIGHステートにピンをアサートしてフラグを立てる。ECCロジックは、読み込みした損傷データを、そのデータの元データがメモリ内で損傷状態のままであっても、訂正を行える。読み込みサイクル中にシングルビット エラーが検出および誤り訂正が行われない場合、ERRピンはアサートされない。

あるデータ ワード内で一度SEUが発生すると、それの影響により同じワード内である一定期間継続的にSEUが発生することがある。これは、同じデータ ワード内のMBUが要因の場合がある。MBUの検出および訂正は、サイプレスのECCアーキテクチャではサポートされていない。ERRピン搭載のデバイスでも、MBUのフラグは立たない。しかしながらこの問題は、SBUが検出されERRピンがフラグされる度に、システム設計者がメモリ セルをリフレッシュすることで回避できる。こうすることで、複数のSEUがMBUになることを防ぐことができる。

サイプレス65nm SRAMとASIC/FPGA/コントローラ間のインタフェース

サイプレスの65nm非同期SRAMのうち、型番に「CY62167GE30」のように「E」を持つものは、ERRピンを持っている製品である。前述の通り、このERRピンを使用すると、システム設計者は、読み込みサイクル中のSRAMのECCロジックの出力をモニタリングすることができる。読み込みサイクル中に、シングルビット エラーが発生しなかった場合はERRピンがアサートされない。SRAMで読み込みが可能な32ビットのワード内でシングルビット エラーが発生すると、ERRピンはその読み込みサイクルにHIGHをアサートする。書き込みサイクルやチップのディスエーブル サイクル中は、ピンはHI Zステートとなる。このERRピンを使用することで、システム設計者はSRAM内のデータの品質を監視できるようになるのである。

ERRピンのインタフェース

ERRピンを搭載していないサイプレスのSRAM製品は、システム上ではレガシーSRAMのようにインタフェースされる。ERRオプション付きのSRAMでは、システム設計者はERRピンをシステム上に正しくインタフェースする必要がある。ERRピンがシステム上で使用されていない場合は、解放されたままになる。ここでは、SRAMを使用する際の3つのベーシックなシナリオにおけるERRピンのインタフェースについて解説する。

SRAMを1個搭載したシステム

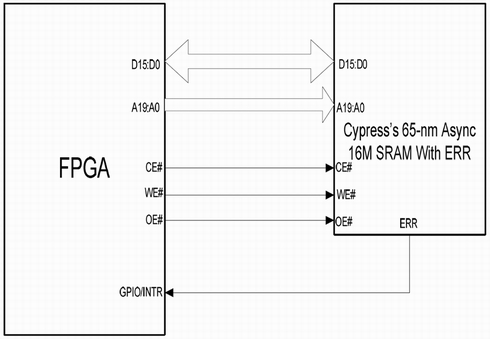

SRAMデバイスを1個のみをボード上のコントローラまたはASIC、FPGAにインタフェースするシステムでは、ERRピンはGPIOやASICのInterruptピンに接続される。各読み込みサイクルでは、コントローラはERRピン出力をモニタリングする。ERRピン上のHIGHが検出されると、ASICはソフトウェアのサブルーチンを起動し、正しいデータを再書き込みする。図2はそのコンフィギュレーションを表している。

帯域幅の拡張

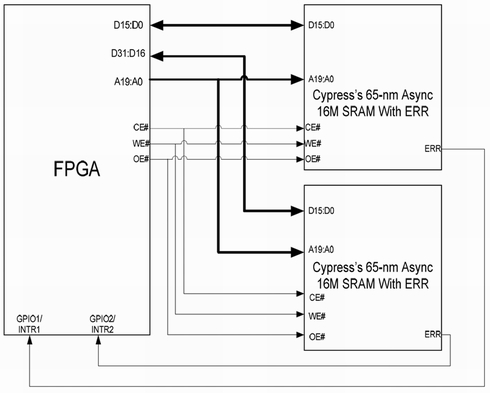

新世代のコントローラは32ビットのデータ インタフェースを持っている。そのようなアプリケーションでは、システム ソフトウェアはデータバス幅を、サイプレスのERRピン搭載の65nm SRAMを使用して拡張することができる。システム ソフトウェアは、ERRピンを別々にモニタリングする必要がある。そこで、2個のx16 SRAMを32ビット バス コントローラへインタフェースするよう設計する。図3は、そのインタフェース技法を表している。2個の1M×16(16Mビット)SRAMを帯域幅拡張モードでインタフェースすると、1M×32(32Mビット)のメモリ スペースが確保できる。

深度の拡張

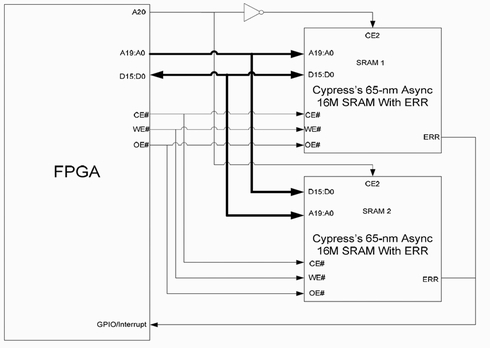

メモリ重視のアプリケーションでは、SRAM内の使用可能容量が、アプリケーションのメモリ要求に満たない場合がある。そのようなケースでは、サイプレスの65nm SRAMを使用することで深度の拡張を実施することが可能である。2個の1M×16(16Mビット)SRAMを深度拡張モードでインタフェースすることで、2M×16(32Mビット)のメモリ スペースを確保できる。ディスエーブルSRAMデバイスは、HI-ZステートのERRピン用に開放しておくことで、アクティブなSRAMが正しく組み込まれたERR信号をドライブできるのである。

サマリー

Single Event Upset(SEU)は、ビット アップセットの点でSRAM内でのデータ格納の脅威となる。エラー検出および訂正機能をシステム ソフトウェア内またはシステム レベルで実施するには、PCBの大きさやタイミング性能の観点でペナルティとなり得る。サイプレスの65nm非同期SRAMは、シングルビット エラー訂正機能のSRAMへの実装にかかる負荷を削減する。オプションで利用可能なERR機能では、SRAMデータのシングルビット エラーのモニタリングが可能で、破壊されたデータはリフレッシュすることでデータ インテグリティを維持できる。サイプレスの最新ECC付き16Mビット非同期SRAMを使用したソフトエラー軽減については、アプリケーション ノートAN88889でも紹介している。

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本サイプレス株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年7月22日

注目記事

いよいよ普及期を迎える「USB 3.0 SS」。そこにはどんな市場が広がっているのだろうか。期待が高まる新規格だが、今すぐに使用可能なUSB 3.0 SS開発ツールは、思ったほど多くはない。ハード/ソフトウェア両面でユーザビリティに優れ、ストレスなくUSB 3.0 SSデバイスを開発できる環境とは?

組み込みシステムは、要求される機能を実現する上で最適なデバイスを選択する必要がある。マイコンとアナログ回路が混在する組み込みシステムにおいて、CPLD/FPGA/マイコン/PSoCそれぞれどのようなメリット、デメリットがあるかを比較してみよう。

世界にひとつしかないASICが供給中止になったら……。ASICの代替を時間をかけずに実現するのが「フィールド プログラマブル デバイス」だ。中でもアナログ混載や小規模ロジックには、サイプレスの「PSoC」が最適解となるだろう。

等式1:ハミング コード式

等式1:ハミング コード式