モデルベースデザイン手法を使ったProgrammable SoCの協調設計【実践編II】:HDLコード生成から統合検証まで(4/5 ページ)

8.Programmable SoC統合検証

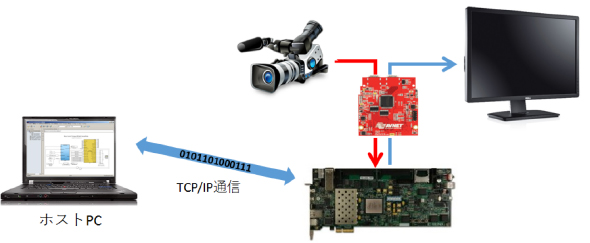

最初にCコード生成、実装を行う際にはエクスターナルモードの使用をお勧めします。これは、ホストPCとプロセッサがTCP/IPで通信しながら実機実行するためのプロトタイプ検証用機能です。このエクスターナルモードでは、Simulinkモデルとプロセッサのメモリはリンクされており、モデル上のブロックパラメーターを変更すると、プロセッサ上のブロックパラメーターに相当するメモリ値が書き換えられます。

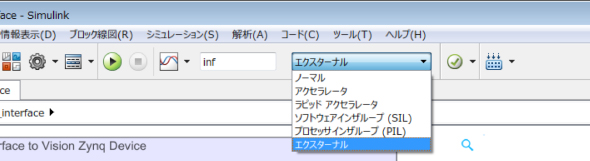

また、モデル上にあったScopeなどの可視化機能も有効で、プロセッサ上で取得される信号をホストPC上のScope画面上に、あたかもシミュレーションであるかのように表示できます。エクスターナルモードを活用することで実機でのユースケース検証、パラメーターチューニング、デバッグを効率的に行うことができます。エクスターナルモードで実行するには、図16に示すように、実行モードのドロップダウンリストを選択します。また、エクスターナルモードの動作イメージを図17に示します。

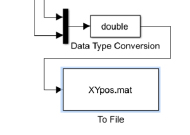

実行モードをノーマルに戻し、コード生成を実行すると、スタンドアローンで動作するようになります。スタンドアローン実行時においては、図18に示すように、SimulinkのTo Fileブロックを接続した状態でコード生成すれば、ARMのLinux OS上で、信号のロギングが行われ、オフラインで実行過程の様子を解析できます。

まとめ

本稿ではモデルベースデザイン手法を使って画像処理によるオブジェクト検出とトラッキングのアルゴリズムをProgrammable SoCのプロセッサとFPGAに実装する流れを解説しました。モデルベースデザインにより、ソフトウェア、ハードウェアの垣根を越えて機能仕様を検討し、そこからそれぞれのコンポーネントをソフトウェア、ハードウェアに落とし込むことで、仕様と実機動作が異なるといったギャップを解消し、不具合による手戻りを抑えられます。

使用ツール一覧

MATLAB R2016b / Simulink, Stateflow, Simulink Test / Fixed-Point Designer / Signal Processing Toolbox, DSP System Toolbox / Image Processing Toolbox, Computer Vision System Toolbox / HDL Coder, Vision HDL Toolbox / MATLAB Coder, Simulink Coder, Embedded Coder / HDL Coder Support Package for Xilinx Zynq-7000 Platform / Computer Vision System Toolbox Support Package for Xilinx Zynq-Based Hardware / Embedded Coder Support Package for Xilinx Zynq-7000 Platform / Xilinx Vivado 2015.4

Copyright © ITmedia, Inc. All Rights Reserved.

図16:エクスターナルモードの選択

図16:エクスターナルモードの選択 図17:エクスターナルモードの動作イメージ

図17:エクスターナルモードの動作イメージ 図18:信号のロギングを行うTo Fileブロック

図18:信号のロギングを行うTo Fileブロック