完全統合型の信号/電源アイソレーターを用いた低放射の実現:信号と電源の絶縁をワンチップで(3/4 ページ)

手順4:サイド1とサイド2の層間コンデンサーの利用

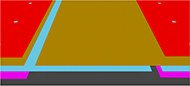

先ほど述べたように、サイド1からサイド2に流れるコモンモード電流と大きなリターンループが絶縁システムでの放射の主な原因です。電流ループを最小にする方法の1つが、サイド1とサイド2の間に高電圧コンデンサーを追加し、ICのできるだけ近くに配置することです(図8)。

このような用途に適したコンデンサーは、電源でよく使用される高電圧Y2コンデンサー(表面実装デバイス(SMD)もしくは適切なクリーページ、クリアランスレベルのリード付きデバイス)などです。プリント配線板(PCB)上でY2コンデンサーを使用する場合、コンデンサーの寄生インダクタンスとともにコンデンサー両端でリードインダクタンスが発生し、200MHzを超える周波数ではコンデンサーとして機能しなくなります。低インダクタンスの容量を作成する方法の1つが、PCB内部の層をオーバーラップする方法です。

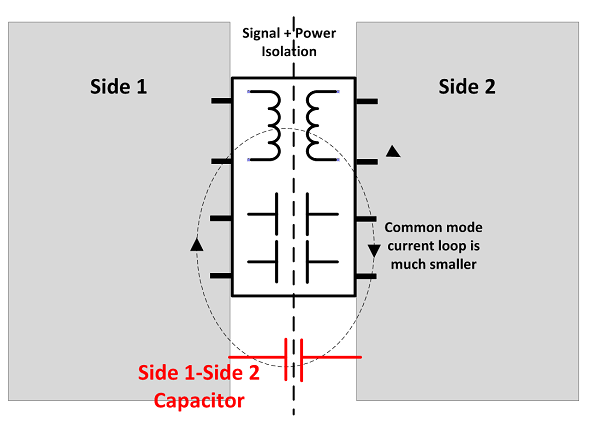

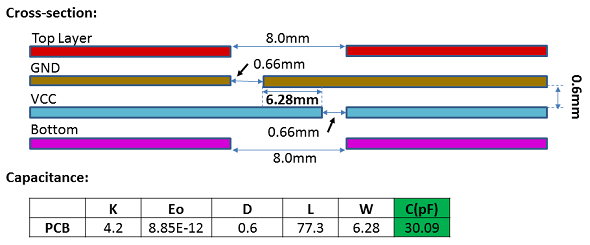

4層PCBで、上層が信号、2層がグランド、3層がVCC、下層が信号となっているものを考えてみましょう。システム絶縁のため、PCBの層は、サイド1の層(Signal1、GND、VCC1各層を形成)とサイド2の層(Signal2、GND2、VCC2各層を形成)の2グループに分けられます。内部の基準層(GND、VCC)を絶縁バリアの両側に拡張(図9)し、内部の層にオーバーラップを作成します。

このオーバーラップ領域は、GND1とVCC2層の拡張によって形成され、2層間のFR4材質が誘電体となって、GND1とVCC2間にスティッチング容量を生成します。高速過渡コモンモード電流に対しては、GNDとVCC基準点は、(AC解析と同様に)同一基準と見なされます。従って、層間スティッチング容量は、サイド1とサイド2の基準点間に形成されます。図10は、4層PCB内部に生成された層間スティッチング容量を立体的に表したものです。

サイド間に形成される等価容量は、式1を用いて求められます。

ただし、ε=ε0εrとします。Ciは層間スティッチング容量、ε0は空気の誘電率(8.854pF/m)、εrは誘電体の比誘電率(FR4では4.2)、Aはオーバーラップする面積、dはGND層とVCC層の間隔です。

式1から図9のPCBの層間スティッチング容量Ciを求めると、約30pFとなります。

システム全体の絶縁性能を満たすには、絶縁バリア上に適切な間隔でスティッチング容量を形成しなければなりません。この間隔は、最終装置の電気的安全規格と動作電圧条件によって決定されます。機能絶縁または基本絶縁が定義されたシステム規格の多くには、同じまたは異なるプレーン上のサイド1とサイド2の層間の最小間隔の規定がありません。そのようなシステムでは、容量を最大にするために、オーバーラップする領域間の間隔を最小にすることが最善です。また、バリアに加わる予測動作電圧と、絶縁材料の絶縁耐力も考慮しなければなりません。

安全システム用および強化絶縁を持つシステム用の規格では、同じプレーン上および異なるプレーン上の両方についてサイド1とサイド2の層間の最小間隔要件が規定される場合があります。300VRMS未満のシステムでは0.4mm間隔、300〜600VRMSのシステムでは0.6mm間隔にすれば、大半の標準規格を満たします。標準化団体では、この間隔に加えて、一時過電圧とサージ電圧について規定しています。例えば、国際電気標準会議(IEC)66010-1では、3510VRMSで5秒間の耐圧試験に加え、300〜600VRMSの商用電源電圧の強化絶縁に対しては6400VPEAKのサージまたはインパルス試験を義務付けています。絶縁耐力に留意して、これらの電圧に耐える層間の間隔を設計する必要があります。例えば、FR4の絶縁耐力は20kV/mmです。

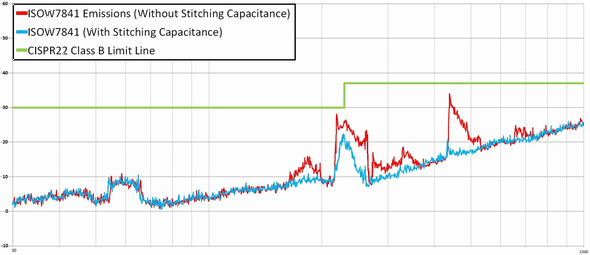

図11は、層間スティッチング容量の使用で放射が減少することを示しています。2つのサイド間に30pFのコンデンサーがあるだけで、全周波数にわたって10〜20dBの改善が可能です。スティッチング値が大きくなれば、放射の減衰量も次第に大きくできます。

バリアの間隔を維持する以外に、PCBのエッジは特に注意する必要があります。エッジでは、プレーンが空気にさらされる可能性があります。反対の電圧が基板のエッジに接近するため、エッジに沿って電界ひずみ、さらには空気の絶縁破壊が生じるかもしれません。鋭いエッジやコーナーは、周辺の電界強度を増加させて空気の絶縁破壊の一因となるため、高電圧インパルス試験で絶縁破壊経路が生じる恐れもあります。このような事態を避けるため、PCBのエッジでは内部層を切り詰め、鋭いエッジを三角形にカットして修正し、電荷密度を分散させます。そのような実装例を図12、図13、図14に示します。コーナーとプレーンを丸めることで、ソリューションをさらに改善できます。

誘電体で完全に囲まれたPCBの内部層では(先ほど述べたように)比較的狭い間隔が許されますが、信号の上層と下層ではもっと広い間隔を保つ必要があります。この間隔は、予測される一時過電圧、インパルス電圧、高度や汚染度などの環境条件に基づいて決定されます。

Copyright © ITmedia, Inc. All Rights Reserved.

図8:サイド1とサイド2間の高電圧コンデンサーによってコモンモード電流のループ面積を縮小

図8:サイド1とサイド2間の高電圧コンデンサーによってコモンモード電流のループ面積を縮小 図9:層間スティッチング容量を持つPCB層の断面図

図9:層間スティッチング容量を持つPCB層の断面図 図10:層間スティッチング容量を持つPCB層の立体図

図10:層間スティッチング容量を持つPCB層の立体図 図11:スティッチング容量30pFがある場合とない場合の「ISOW7841」(5V入力、80mA電流負荷)

図11:スティッチング容量30pFがある場合とない場合の「ISOW7841」(5V入力、80mA電流負荷)