LVDS PHY製品と伝送路の設計(その1):高速シリアル伝送技術講座(6)(1/5 ページ)

LVDS PHY(物理層)製品を使用する上で必要な一般的な知識とともに、伝送路の設計方法について詳しく解説していきます。

高速シリアルデバイス:インタフェーステクノロジーの選択

高速伝送を使用するシステムを設計する際、どのようなインタフェースステクノロジーを選択するかは基本設計時の重要な課題です。

実装する高速インタフェースが、他社製品との相互接続性を必要とするのであれば、規格に準拠するデバイスを選択することになるでしょう。逆に他社製品との相互接続が必要なく、基板内や筺体内、機器間の接続で、外部へ解放しない高速インタフェースでは、以下の手順により高性能でオーバーヘッドの少ない、またパワー効率にも優れたシステム設計を行うことができます。

最初の選択はトポロジ(接続形態)です。必要なトポロジは1対1(=1:1)、1:NそれともN:Nでしょうか。パラレル信号をシリアルに変換するSerDes(シリアライザ・デシリアライザ)が必要な仕様でしょうか。

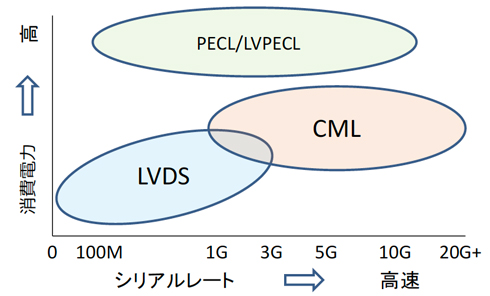

次に選択しなければならないのが、帯域とパワーバジェット(消費電力の割り当て)です。帯域は数百Mビット/秒(bps)で十分でしょうか。それとも10Gbpsが必要になるでしょうか。トータルの消費電力からインタフェースに割り当てるパワーはどの程度でしょう? LVDSのローパワーが必要なのでしょうか、それとも高消費電力のCMLも許容できるのでしょうか?

LVDSはさまざまなアプリケーションに使用されている、高速、低消費電力で、受信可能な差動信号の範囲が広いなどの特長を持った物理層テクノロジーです。今回は前回に説明した3種類の高速デバイスの1つであるLVDS PHY(ファイ)製品から説明していきます。

LVDS PHY(物理層)製品:低コストで汎用性に富んだ物理層インタフェース

1995年11月にデジタル信号伝送の物理層規格としてTIA/EIA-644(Low Voltage Differential Signaling)が発行されました。当時もコンピュータシステムの高速化が課題の1つでしたが、信号伝送ではLVDSを使用することでローパワーかつ高速化を容易に実現できたことから、各半導体メーカーからLVDS物理層を採用したさまざまな製品が販売され、高速化が必要な多くのアプリケーションで使用されるようになっていきました。

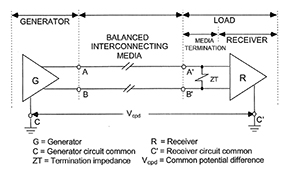

LVDSは図1のようにアプリケーションを限定しない、ローパワー、低EMI、高速、長距離伝送が可能な信号伝達の単純な物理層の汎用インタフェースとして、また上位層には規定がなく、異なるメーカーのデバイス同士でもTTL/CMOSと同じような物理的な相互接続が可能になるように作られました。

策定の際には、その後のデジタル通信の高速化を見込んで他の高速規格からも参照されることも意図して作られました。また2001年にANSI/TIA/EIA-644-Aとして更新されています。

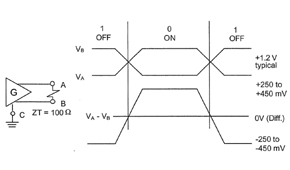

図1:TIA/EIA-644 LVDS 送受信の構成と出力仕様 (クリックで拡大)

図1:TIA/EIA-644 LVDS 送受信の構成と出力仕様 (クリックで拡大)出典:TIA/EIA-644-A Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits

TIA/EIA-644-A(LVDS)は差動ドライバーの出力特性と差動レシーバーの入力特性を定義しています。差動上の1, 0信号の論理条件やDC/AC特性は規定されていますが、物理的なケーブルやその長さ、コネクターに関しては規定していません。仕様上0Hzからアプリケーション上の推奨最大値の655Mbps(無損失伝送路での論理的最大値1.923Gbps)まで使用でき、その帯域内であれば自由に周波数の選択が可能です。そのため設計の自由度が高い高速伝送規格と言えるでしょう。また上限周波数が3Gbps程度の規格を超える製品もあります。

LCD(液晶ディスプレイ)パネルインタフェースとして有名なLVDSですが、このアプリケーションではLVDS物理層を使用したSerDesを意味しています。そのためLVDS SerDesというべきですが、略称としてLVDS SerDesをLVDSと呼んでいます。

その他のテクノロジーとの比較

高速差動I/OのテクノロジーとしてはLVDSの他に連載第3回で説明したPECL系やCMLもあります。ドライバーでは電流値は異なりますがLVDSと同様に定電流源駆動で常に電流を流しているため、シングルエンドCMOSロジックのようにスイッチング時に大きい貫通電流が流れず、不要輻射にも有利です。また差動信号を使用すると差動ペア配線が電磁気的に密結合しているので、受信可能なコモンモード電圧範囲内のコモンモードノイズは、受信側の差動増幅器でPositive-Negativeの計算によりキャンセル可能になります。

図2は各テクノロジーのシリアルレートと消費電力の関係を示しています。図2のようにPECL系やCMLはLVDSよりも消費電力が高いですが、高速性に優れています。残念ながらPECL系とCMLではLVDSのような相互接続のための物理層規格がなく、多くがAC結合で送信側と受信側を接続しています。コンデンサーを介したAC結合を使用すると、コモンモード電圧の制限がなくなりますが、DCが通らないためシリアルデータはDCバランス(1や0の数が均等)やランレングスの短い(1や0の連続数が少ない)コーディングが必要になり、実装がLVDSのように容易ではなくなります。

3Gbps程度で動作する高速のLVDS製品では、伝送路での高帯域信号の損失を補償するため、送信側ではエンファシスドライバー(プリエンファシスもしくはデエンファシス)、受信側ではイコライザを実装している製品も多くあります。

Copyright © ITmedia, Inc. All Rights Reserved.

図2:LVDS,CML PECL系I/O シリアルレートと消費電力比較

図2:LVDS,CML PECL系I/O シリアルレートと消費電力比較