ニュース

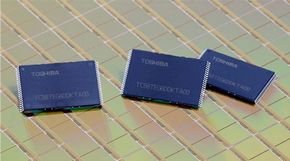

東芝、19nmプロセスを改良し「世界最小」の64Gbit容量品を発売:東芝 NANDメモリ

東芝は、改良版19nmプロセスを用いて「世界最小」という64Gbit容量の2ビット/セル構造NAND型フラッシュメモリを2013年5月から量産すると発表した。改良版19nmプロセスは、従来プロセスと最小線幅は同じだが、最大線幅を19nmに近づけた。

東芝は2013年5月21日、19nm半導体製造プロセスを改良した「19nm第2世代プロセス」を用いて1セル当たり2bitのデータを格納する2ビット/セル構造のNAND型フラッシュメモリの64Gbit容量品を開発し、5月から量産すると発表した。

従来、東芝がNANDメモリに適用していた19nmプロセスでは垂直方向、水平方向のいずれかの線幅が19nmで、残るもう一方の線幅が26nmとなっていた。今回、新製品に適用した19nm第2世代プロセスは、最小線幅19nmは変わらないが、もう一方向の線幅を19.5nmに縮小させたという。

新製品は、19nm第2世代プロセスの適用と周辺回路の工夫により、2ビット/セル構造のNANDメモリの64Gbit容量品として「世界最小」(同社)とする94mm2のチップサイズを達成したという。加えて、東芝独自の高速書き込み方式により毎秒25MBの書き込み速度を実現した。同社では2ビット/セルのNANDメモリとして「世界最速クラス」としている。

関連記事

SanDiskが19nm世代のNANDフラッシュをサンプル出荷へ、2ビット/セルで64Gビット

SanDiskが19nm世代のNANDフラッシュをサンプル出荷へ、2ビット/セルで64Gビット

SanDiskは19nmプロセス技術で製造するNAND型フラッシュメモリを今四半期中にサンプル出荷する。2011年の下半期には量産を始める予定だ。 ECCを搭載したSLCタイプNANDフラッシュ、4Gビット品と8Gビット品を用意

ECCを搭載したSLCタイプNANDフラッシュ、4Gビット品と8Gビット品を用意

東芝の「BENAND」は、ECC回路を搭載するSLCタイプのNAND型フラッシュメモリ製品である。ECC回路の訂正能力は、512バイト当たり4ビットとなっている。 ハンダフロー実装に対応するベクトルエンジン搭載少ピンマイコン

ハンダフロー実装に対応するベクトルエンジン搭載少ピンマイコン

東芝は、「ARM Cortex-M3」を搭載するマイコン「TX03シリーズ」として、単層基板、ハンダフロー実装が使用できるベクトルエンジン搭載製品「TMPM372FWFG」を発表した。家電やFA機器などでの採用を見込む。

Copyright © ITmedia, Inc. All Rights Reserved.