工場内にも広がるシリアルネットワーク(2/3 ページ)

効果的なトポロジとは?

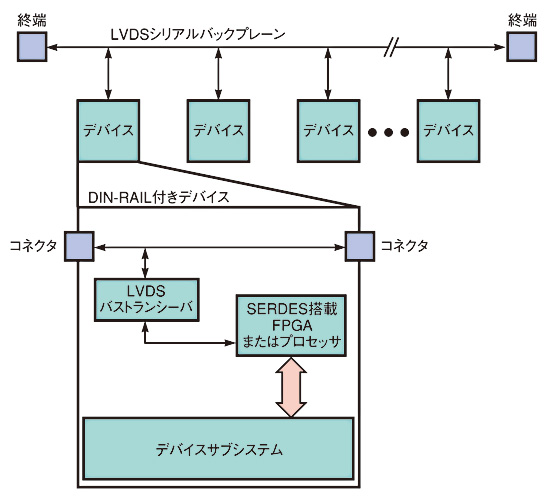

どのようなトポロジが最も効果的なのか?選択肢には、マルチドロップバス、冗長マルチドロップバス、ポイントツーポイントバス、そしてよく見られるリングトポロジがある。マルチドロップ(またはマルチポイント)バスは多くのバックプレーンで使用されており、シングルプロセッサシステム、マルチプロセッサシステムのどちらにも適している。LVDSを選択したら、各ボードのLVDSトランシーバに二重終端伝送線を使用することになるだろう。個別のトランシーバを使用することには2つの利点がある。1つは、トランシーバをコネクタの近くに配置できるため、接続の切れ目からの近端反射を軽減できること。もう1つは、FPGAに集積されたドライバよりもトランシーバの方が頑強なことだ。また、欠陥品を交換するときも、100米ドルもするFPGAに比べれば安い。このトポロジでは、メッセージによってボード上のドライバが駆動され、シリアルパケットがバックプレーンに送信される。他のすべてのデバイスがリスナーとなり、伝送されたパケットを受信する。バス共有トポロジには大抵なんらかのトラフィック制御が必要だ。簡単なのは、共通アクセスラインにその他の配線をつなげ、あるデバイスが通信を要求したら他のデバイスはトークできないことを、すべてのデバイスに通知する方法である。あるいは、親機/子機構成にして、マスターコントローラが要求した場合にのみ通信を許可する方法もある(図1)。

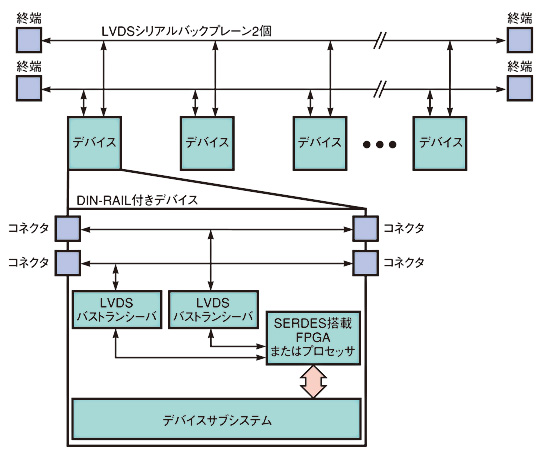

マルチドロップバスは実装が簡単だが、短絡や終端抵抗の損失、バスドライバのハングなど、たった1つの障害が発生しただけでバス全体がダウンする可能性がある。このような障害は、工業環境では致命傷になりかねない。障害の発生が許されない精油所を考えてみればわかるだろう。この問題を解決する簡単な方法は、2本のバスを使用することだ。1本がダウンしても、もう1本が生きている。このような冗長性があることに加え、ネイティブモード(通常動作)では2倍の帯域幅を使用できる。2本のバスのうち1本に障害が発生しても帯域幅が半分になるだけで、システムは制限モードで機能し続けることが可能だ。この方法の欠点は、コストと複雑さが増すことである(図2)。

バス障害を回避するもう一つの方法として、イーサネットに見られるポイントツーポイントトポロジを使用する方法がある。このトポロジでは、すべてのデバイスにコントローラと通信するための専用バスが割り当てられる。1つのデバイスまたはバスに障害が発生しても、他のデバイスは影響を受けることなく動作し続ける。

しかしローカルバックプレーンでは、機械的な相互接続の問題がある。DINレールに取り付けるときのように、デバイスを相互に接続するような場合には、パススルー接続が必要になるため、相互接続の数はむしろ増えてしまう。配線数が増えるなら、バックプレーンのポイントツーポイントトポロジにメリットはない。

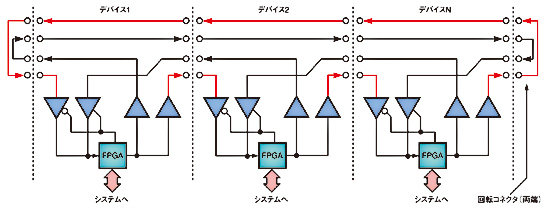

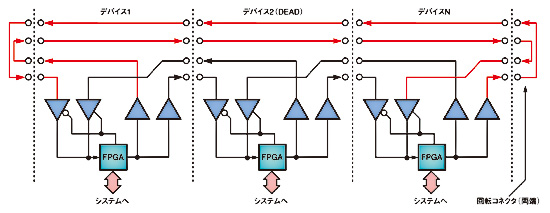

一方、リングトポロジはセルフヒーリング方式で自動的に自らを分割できる。この方法はトークンリングやこれに類似するネットワークで採用されている。バックプレーンの実装では、システムにリングが組み込まれる。このトポロジでは、DINレール上でモジュールを数珠つなぎにすることも可能だ(図3)。デバイスまたは接続に障害が発生すると、リングはもとの状態に戻り、障害が発生したデバイスまたは接続を分離することができる(図4)。リングトポロジの物理的実装にかかる費用は、インターフェース部分を除けばデュアルマルチドロップバスアーキテクチャとそう変わらない。リングで使用されるのはドライバとレシーバのみで、トランシーバは使用されない。しかし、リングを完成させるには別に2本の受動バスが必要となる。ドライバは常に駆動している。しかし、このデバイスは2本の受信バスのどちらでも選択できるため、イネーブル信号によって目的のバスを選択する必要がある。あるいは、FPGA上の2つのデジタル入力でバスを選択することも考えられる。この方法をとっているコンポーネントの例としては、デジタル信号でレシーバを選択する米National semiconductor社製DSLV049、DS90LV 027/28、DS90LV019トランシーバがある。

リングトポロジの面白いところは擬似ポイントツーポイント接続を使えることだ。この方法ではパケットトラフィックが単方向性のため、バスアクセスの必要がない。しかし、すべてのモジュールがすべてのパケットを処理しなくてはならないという欠点もある。設計者は、ショートバッファを使用して、インターフェースの制御ロジックでこのプロセスを自動化することにより、ストア・アンド・フォワード方式を実現することができる。デバイスはパケット全体をストアする必要はないが、検査のためにヘッダだけはストアする必要がある。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 多くのバックプレーンには、各ボードでLVDSトランシーバを相互接続するマルチドロップシリアルバスが使用されている。

図1 多くのバックプレーンには、各ボードでLVDSトランシーバを相互接続するマルチドロップシリアルバスが使用されている。  図2 デュアルマルチドロップバスを使用すれば、1つの障害が発生してもシステムを稼動させられると同時に、システム帯域幅も倍になる。

図2 デュアルマルチドロップバスを使用すれば、1つの障害が発生してもシステムを稼動させられると同時に、システム帯域幅も倍になる。  図3 この3つのデバイスを使用したリングトポロジの例は、セルフヒーリングと自動パーティショニングを示している。

図3 この3つのデバイスを使用したリングトポロジの例は、セルフヒーリングと自動パーティショニングを示している。  図4 FPGAバスコントローラを使用したリングトポロジでは、TCP/IP-over-Ethernetバックプレーンを容易に実装できる。

図4 FPGAバスコントローラを使用したリングトポロジでは、TCP/IP-over-Ethernetバックプレーンを容易に実装できる。