高性能かつ低消費電力のLSIを実現する技術:デュアルスレッショルド電圧とパワーゲーティング(1/2 ページ)

デュアルスレッショルド電圧とパワーゲーティングの設計フローを用いれば、リーク電流とパフォーマンスの両方を、少ない労力で調整できる。

スレッショルド(閾(しきい)値)電圧VTHが異なる2種類のゲートを使用する設計最適化フローは、大部分が自動化されており、かつ電力とタイミングの両方で優れた結果を得られる手法である。VTHを落としてもパフォーマンスが上がらないばかりか、(リーク電流による)静的電力が増えてしまうVDSM(very deep submicron)チップでは、このデュアルVTHを用いる手法が不可欠になってきた。

実際、微細化技術の進化に伴ってリーク電流は著しく増加しており、65nmプロセスではチップ電力の50%にも達している。このリーク電流の急激な増加は、その機器がバッテリ駆動かどうかに関係なく、ほとんどの設計で受け入れられないものだ。そのため、パフォーマンスとリーク電流のバランスをとる設計最適化フローが注目されている。

設計要件に基づいてパフォーマンスとリーク電流を最適化する一般的なフローは3つある。これらのフローは、パワーオンモードの設計で、最小限のリーク電流、最大限のパフォーマンス、最適なチップ面積とツール処理時間を実現することを目的としている。スタンバイモードではどうしてもリーク電流が増えるため、これらのフローにはスタンバイリーク電流を最小限に抑えるための方法も取り入れられている。

リーク電流の削減フロー

デュアルVTH方式では2つのセルライブラリを使用する。1つは、伝搬遅延が少なくリーク電流の大きい低VTHセル用、もう1つは遅延が大きくリークが少ない高VTHセル用である。タイミングクリティカルなパスで低VTHセルを使い、その他のパスで高VTHセルを使って設計を最適化することにより、速度を最大限に上げ、リーク電流を最小限に抑えることができる。

この最適化の効果は、真にタイミングクリティカルなパスを特定して、2つのライブラリのタイミングがパスに及ぼす影響を正確に計算できるかどうかにかかっている。必要なタイミング精度を得るには、パス遅延計算にセル配置情報とネット配線情報に基づく相互接続遅延を含める必要がある。そのため、物理合成における二次パスの混在VTH設計の最適化では、次の3つのフローが推奨されている。

■mini-cutフロー

3つのフローのうちリーク電流を最小限に抑えられるが、より多くのセルと動的電力を必要とする一方でパフォーマンスが低い。

■max-cutフロー

最少のセル数と動的電力で最高のパフォーマンスを達成できるが、3つのフローのうちでリーク電流が最も大きい。

■max-cut II フロー

リーク電流とチップ面積のバランスを取ることで上記2つのアプローチの折り合いをつけたもので、ツール処理時間やメモリー容量も考慮している。

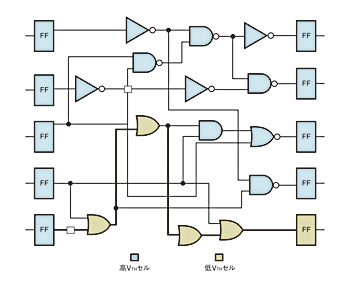

1つ目のフローは、最初に組み合わせ回路内のすべてのセルに高スレッショルド電圧が割り当てられる反復min-cutアルゴリズムを使用する。高VTHトランジスタのパフォーマンスの低下により、通常は遅延条件の違反が発生する。しかし、初期設計でのリーク電流は最も少ない。次にこのアルゴリズムは、スレッショルド電圧がLowに切り替わることでパフォーマンスが向上し、遅延条件を満たすことができるエッジの最小サブセットを特定する。最小重みカットに基づくmin-cutグラフアルゴリズムによってこれらのエッジが特定される。このカットでは、低VTHに切り替わることで電力増加を最小限に抑えられる。図1は、min-cutアルゴリズムを使用したデュアルVTHの割り当ての例を示している。

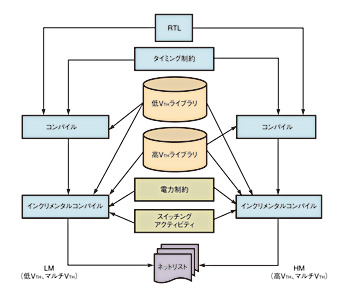

リーク中心の設計最適化フローとして考案されたmin-cutアプローチでは、リーク電流を最小限に抑える回路を設計できる。図2の右半分がこのフローを示している。高VTHライブラリを使用した最初の最適化の後、通常はタイミング違反が起こる。その後、低VTHセルと高VTHセルの両方を使用した最適化により、タイミングクリティカルなすべてのパスが特定され、それらのパスにあるセルが低VTHセルに置き換えられる。さらに、低VTHセルへの置き換え後も違反となるパスを修正するために、合成ツールによってローカル設計の最適化が実行される。

反復min-cutアルゴリズムとは異なり、反復max-cutアルゴリズムは最初に組み合わせ回路内のすべてのセルに低VTHを割り当てる。低VTHセルは速いため、この実装ならば定義されている遅延条件を余裕で満たせるが、リーク電流が増える。次にこのアルゴリズムは、スレッショルド電圧が高い方に切り替わることで遅延条件に違反することなくリーク電流を削減できるエッジの最大サブセットを特定する。max-cutグラフアルゴリズムは、高VTHへの切り替えによって最大のリーク電流を削減できることを示す最大重みカットに基づいてこれらのエッジを特定する。図1の左半分が示すこのアルゴリズムは、基本的には前述のフローと同じように機能するが、低VTHライブラリと高VTHライブラリを逆の順序で使用する。

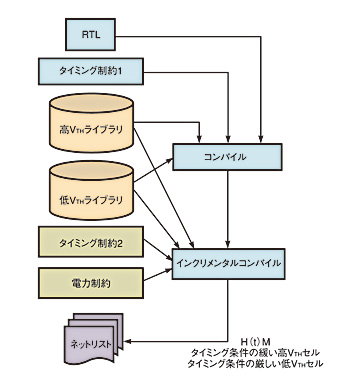

3番目のアプローチは、ツール処理時間とメモリー容量の問題を軽減するもう1つのmax-cutアルゴリズムである(max-cut IIと呼ぶ)。このmax-cut IIアルゴリズムは、まず設計のすべてのセルを高VTHセルにして、タイミング条件に違反するクリティカルサブ回路を特定する。そして、タイミング条件を満たすために、クリティカルサブ回路内のすべてのセルが低VTHに切り替えられる。次に、通常のmax-cutアルゴリズムが、再び高VTHに戻しても遅延違反を起こすことのないエッジを特定する。したがって、max-cut IIは基本的にクリティカルサブ回路のみにmax-cutアルゴリズムを適用するため、最適化される回路のサイズを大幅に縮小できる。したがって、max-cut IIアルゴリズムのフロー実装では、通常のmax-cutアプローチよりもチップ面積を減らし、ランタイムを最適化することが可能である(図3)。max-cut IIフローでは、リーク電流を最小にするために高VTHライブラリを使用して設計を最適化する。しかし、クロック周波数を下げれば、高VTHセルだけではタイミング条件を満たせないタイミングクリティカルパスに対処しなくても、余裕のあるタイミング条件で最適化を行うことができる。この最初の最適化を行った後、クロック周波数を本来のターゲット値に調整して実際のタイミング条件に戻し、低VTHライブラリと高VTHライブラリの両方を使用して設計を少しずつ最適化すればよい。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 リーク電流を削減するこのmin-cut手法では、タイミング条件を満たすために、クリティカルパス内のロジックゲートが合成ツールによって低VTHゲートに置き換えられている。

図1 リーク電流を削減するこのmin-cut手法では、タイミング条件を満たすために、クリティカルパス内のロジックゲートが合成ツールによって低VTHゲートに置き換えられている。  図2 このフローチャートの右側と左側は、それぞれmin-cutフローとmax-cutフローの例を示している。唯一の違いは、一方は最低リーク(高VTHセル)で始まり、他方は最低遅延(低VTHセル)で始まることだ。

図2 このフローチャートの右側と左側は、それぞれmin-cutフローとmax-cutフローの例を示している。唯一の違いは、一方は最低リーク(高VTHセル)で始まり、他方は最低遅延(低VTHセル)で始まることだ。  図3 max-cut2手法は図2のmax-cutフローと同じだが、クリティカルサブ回路のみを変更する。ツール処理時間も短縮される。

図3 max-cut2手法は図2のmax-cutフローと同じだが、クリティカルサブ回路のみを変更する。ツール処理時間も短縮される。