PCI Expressの可能性を探る:基幹系ネットワーク機器の低コスト化と設計期間短縮に向けて(2/4 ページ)

PCIeに適した処理

トランスポート層では、高いデータ転送速度が必要で、大容量チャンネル上での長距離データ転送を行う。しかし、トランスポート層の機器は転送するデータに深く関与しない。そのため、この階層の機器はPCIeには不向きである。

コア層におけるネットワーク機器は取り扱うデータを認識するが、それでもデータとのやりとりは限定されている。一般にコア層ではデータを制御するプレーン(制御プレーン)とデータを処理するプレーン(処理プレーン)が分離されたアーキテクチャを用いる。これらのうち、制御プレーンはシステム内におけるデータの経路を処理プレーンに指示するためのテーブルを管理する。コア層の制御プレーンのような処理にはPCIeが利用できるかもしれないが、処理プレーンでは、パケットルーティングのオーバーヘッドを最小化して高い帯域幅効率を達成するために、独自のバスアーキテクチャやプロトコルが採用される傾向にある。

エッジ層のハイエンド機器は、コア層の機器と同様のアーキテクチャを有する。エッジ層の機器はサービス性を重視したQoS(quality of service:サービス品質)処理を実施し、トラフィックを管理する。エッジ層のローエンド機器は大抵ノードの集合体で、エッジ層のハイエンド機器との間のトラフィック量をできるだけ均一に保ち、エッジ層の帯域幅効率を上げる役割を果たす。この層であれば、制御プレーンと処理プレーンのどちらの要求にもPCIeの性能がしっくりと当てはまる。

アクセス層は、ユーザーがサービスプロバイダへの接続を行う層であり、ここがPCIeに最も適している。この層では、エンドユーザーとの通信にウェブへのアクセス、メールの送受信、マルチメディアコンテンツ(映像、音声)の配信などに対応したさまざまなプロトコルを扱う必要があるため、求められる要件は多種多様となる。また、ユーザーとの通信距離など物理的な条件がこれらの要件に影響を与える。機器の設計では、冗長性の実現方法、ポート数、ノードの容量など、考慮すべき問題が多岐にわたる。設計者は、制御プレーンと処理プレーンを分離するか、トラフィックを結合するかなど、複数の選択肢に対する答えに基づきアーキテクチャを決定しなければならない。

制御プレーンと処理プレーンを分離する場合、2つのバス要件が存在することになる。制御プレーンは、制御レジスタ、カウンタ、テーブル、転送データブロックなどへ頻繁にアクセスする。この状況から、トラフィックの大部分が、中央で管理を行うプロセッサとデータ処理を行う個々のノードとの間で生じることになる。この種のトラフィックには、パソコンのアーキテクチャに由来するPCIeのメモリーマップドアドレッシング構造が適している。

同様に、PCIeは制御プレーンと処理プレーンを統合する場合の要求にも合致する。PCIeの性能であれば必要なデータ転送速度が実現でき、PCIeアーキテクチャによってデータの転送先を指定する前に制御プレーンからデータヘッダーにアクセスしたいという要求にも対応できるためである。

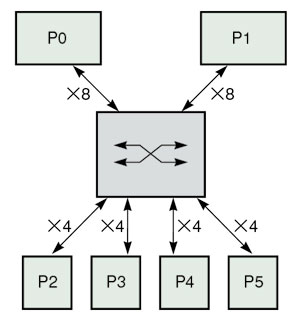

加えて、処理プレーンに対しては、入力ポートと出力ポートのあらゆる組み合わせに対応し、データを高速に転送できなければならないという要求がある。PCIのような従来のマルチドロップ型パラレルバスでは、この要求に十分に応えることはできない。なぜなら、マルチドロップ型バスではクロス接続は可能だが、一度には1つのペアのデバイス間でしか通信することができないからだ。これに対しPCIeはデータパスにスイッチを利用している。スイッチはノンブロッキング、つまり、同時に複数のポートのペア間を接続することができる(図2)。この能力により、PCIeを利用すれば処理プレーンの要件に適したデータフロー構造が実現できる可能性がある。

PCIeの問題点

ここまでPCIeの可能性について論じてきたが、実はPCIeには大きな問題がある。それはネットワーク機器にとって重要な冗長性に関する要件を満たしていないことだ。

ネットワークシステムでは、特に上層において非常に高い信頼性が求められる。ノードが完全に故障してしまうとネットワーク全体が停止する。このような障害が生じると、少なくとも収益が減少し、顧客から不満が寄せられることにもなる。従ってネットワークシステムでは、複数のプロセッサを並行に稼働させることで冗長性を持たせた設計が必要となる。

困ったことに、PCIeではプロセッサのような制御ポイントは1つしか設定できない。パソコンでは、プロセッサがシステム内のそのほかすべてのエレメントを管理/制御する単一のシステム構成を持つ。そのためPCIeは、複数の独立したプロセッサがそれぞれシステム内のリソースにアクセスするような構成はサポートしていない。システムにもう1台プロセッサが存在する場合は、そのプロセッサは1つ目のプロセッサに対してスレーブで動作しなければならない。つまり、そのプロセッサは独自に周辺機器への処理を指示することはできない。同様に、PCIeでは複数のプロセッサがシステムリソースへのアクセスを共有することはできないのである。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 PCIeにおけるスイッチの例 このPCIeのスイッチは、2×8レーン(図上部)または4×4レーン(図下部)の構成で、ポートのペアを接続する。ノンブロッキングスイッチである場合は、ポートの競合がない限り、P1とP3、およびP2とP5のように複数の接続を同時にサポートすることが可能である(提供:NEC)。

図2 PCIeにおけるスイッチの例 このPCIeのスイッチは、2×8レーン(図上部)または4×4レーン(図下部)の構成で、ポートのペアを接続する。ノンブロッキングスイッチである場合は、ポートの競合がない限り、P1とP3、およびP2とP5のように複数の接続を同時にサポートすることが可能である(提供:NEC)。