FPGA⇒ASICを成功に導く8つのポイント(3/3 ページ)

ポイント7 メモリーの初期状態の制御

FPGAのアーキテクチャにおいて特有な処理に、メモリーの初期化がある。ここで行われるのは、アルゴリズムの実行やステートマシンなどの初期化といった簡単な起動処理である。フィルタの係数などの定数をロードする容易な手段でもある。

ASICへの移行で問題となるは、ASICのメモリーの状態が起動時に不定になってしまう場合だ。この問題に対してはさまざまな対処法が存在する。有効な方法の1つは、ASICへの移行時に初期化可能なメモリーを採用することである。メモリーの初期化を行うための専用ソフトロジックまたはラッパーロジックを追加する方法もある。

もう1つの、そして最も容易な方法は、メモリーが初期化されているかどうかに依存しないようにシステムを設計することである。FPGA特有の機能に依存しないよう設計すれば、回路の可搬性がより高まり、ASICへの移行時により多くのオプションを適用可能となる。さらには移行にかかる時間も短縮できる。

ポイント8 同期設計の励行

ASICとFPGAのロジックゲートで同じ性能が得られなくなる原因の1つに遅延の問題がある。たとえアーキテクチャや製造プロセスが同じであっても、遅延を一致させるのは難しい。ましてや、65nmプロセスのFPGAから130nmプロセスのASICへの移行であれば難易度はより高まる。そこで重要となるのは同期設計を適用することである。

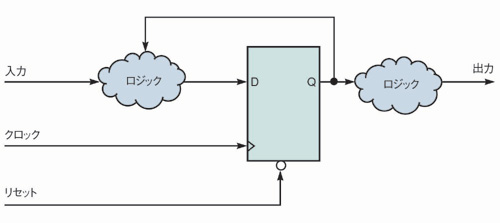

同期回路の最も基本的な考え方は、すべてのフリップフロップに共通のクロック信号線を1つ用意し、すべてのフリップフロップに共通のリセット(またはセット)信号線を1つ用意するというものである(図2)。しかし実際の設計においては、複数のクロックを扱わなければならないことが多い。その場合には、複数のクロック信号が互いに対して任意の時間に変化する可能性があると仮定し、使用するプロセス技術に依存しない方法を入念に検討する必要がある。結果として、さまざまなハンドシェイクプロトコルや独立したクロックで動作するFIFOバッファを持つメタステーブルなフリップフロップを利用しなければならなくなるかもしれない。こうした方法は、異なる実装に移行する際の遅延の問題はシミュレーション時やFPGAによるプロトタイプ開発時には把握しきれないことがあるため、非常に重要である。

当然のことだが、チップ内部でクロックを生成/分岐したり、リセット信号を生成したりするのは極力避けるべきである。そのような信号は、互いに依存関係や遅延を持つことになるので、実装によって違いが生じる可能性がある。問題が起こりがちなのは、電力を削減するためにゲーティドクロック手法を適用するケースである。FPGAにおいて、その高い消費電力を削減するためにこの方法を用いることがあるかもしれない。しかし、ASICの全体的な消費電力は基本的にFPGAのそれよりかなり少ない。従って、ASICではゲーティドクロック手法は不要であるかもしれない。この手法を適用する必要がある場合には、必ず、なぜ必要なのか、すべての場合において正しく動作することをどのように検証すればよいのかということをドキュメントとして残しておくとよい。それを基に、移行を担当するチームとレビューを実施するとよいだろう。

ほかにも、有限ステートマシンの設計において適切なデッドステート処理を加えること、ラッチを避けること、遅延に対する依存性を除くことといった有効な手法がある。これらの手法を採用し、できるだけ製造プロセスに依存しない設計を目標とするとよい。

FPGAでは、ルックアップテーブルを実装することにより高速な複合ロジック機能を実現できる。しかし、プログラマブルに接続される配線部分の遅延が一因で、ASICとは異なる動作になる可能性がある。例えば、小さなグリッチが生成されるような組み合わせロジック回路があったとする。FPGAでは配線部分がローパスフィルタとして機能し、グリッチが減衰する可能性があるが、ASICではそれが次のゲートへと伝送されてしまうかもしれない。仮にその信号がフリップフロップのクロック端子を駆動してしまったりすると、問題が生じる可能性がある。このことからも、同期設計を用いることが良い結果につながることがわかる。クロックやリセット信号上に組み合わせロジックが存在しなければ、そのような問題が生じることはない。

同期設計を行うと、移行後のASICのテストがかなり容易になる。最近では、自動的/半自動的にテスト用ロジックの挿入と検査プログラムのアルゴリズム生成を行うDFT(design for testing)手法が利用されている。より良い方法で設計された回路であれば、DFTツールも最大限に活用できる。それに対し、非同期クロックや、複数のクロック、ラッチ、遅延への依存性を持つ回路では、一般的にテストカバレッジが低下する。

事前の検討が重要

ここまでに紹介した簡単なポイントに留意するだけで、FPGAからASICへの移行をよりスムーズに行えるようになる。ASICへの移行を考えるなら、FPGAの設計を開始する前にASICベンダーに相談してみるとよい。ASICベンダーは、シームレスな移行を実現するための情報や指針を提供してくれるはずである。特に、ASICの開発経験がないなら、ASICベンダーに必ず相談することを推奨したい。ロジックゲートはどれも同じようにできていると思っているかもしれないが、FPGAとASICは厳密な意味で等価なわけではない。FPGAの設計を開始する前に、ASICベンダーを選定して方針を作っておくとよいだろう。

適切なASICプラットフォームをターゲットとし、適切なパッケージの選択や端子定義など、移行にかかわる計画がしっかりと練られていれば、コストを最大限に削減することができる。IPライセンスの問題を前もって把握し、FPGAベンダーの専有IPで実現した機能をどのように変換するのか、または変換しないほうがよいのかといったことを決めておくことにより、移行時の問題を減らすことができる。全体的な品質を高めるために、どのような設計方法を採用し、どのような方法は避けるべきなのかといったことも考察しておくとよい。

Copyright © ITmedia, Inc. All Rights Reserved.

図2 同期回路の基本構成 すべてのフリップフロップに共通の1つのクロック信号線と、すべてのフリップフロップに共通の1つのリセット(またはセット)信号線を用意する。

図2 同期回路の基本構成 すべてのフリップフロップに共通の1つのクロック信号線と、すべてのフリップフロップに共通の1つのリセット(またはセット)信号線を用意する。