ΔΣ型A-Dコンバータの要点(その1):Baker's Best

今回から数回にわたり、ΔΣ変調方式を利用したA-Dコンバータ(以下、ΔΣ型A-Dコンバータ)の構成と動作の要点を解説する。ΔΣ変調方式は、DCから数メガヘルツに及ぶ周波数の信号に対する高分解能のA-D変換方式として最適である。

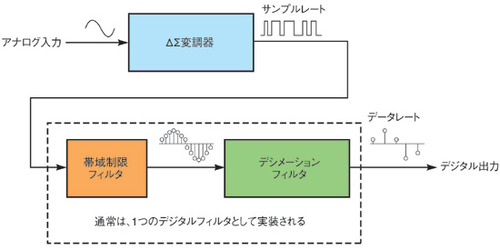

ΔΣ型A-Dコンバータの基本構成は、図1に示すようにΔΣ変調器とデジタルフィルタが直列に接続されたものとなる。ΔΣ型A-Dコンバータの中には、これらの要素のほかにも、さまざまな機能ブロックを持つものがあるが、基本的には図1の構成が中心になっている。

この正弦波信号は、まずΔΣ変調器内部の1ビットのA-Dコンバータによって、本来のサンプルレート(サンプリング周波数)よりも高速にサンプリングされる。つまり、1ビット分解能という極めて粗いレベルで量子化されることになる。言い換えれば、ΔΣ変調器によるこの処理の内容は、入力アナログ信号を高速のパルス波形に変換することである。そのパルス波形において、0の幅と1の幅の比率が入力アナログ信号波形の本来の性質を反映したものとなる。

このように、ΔΣ変調器では粗いレベルで量子化を行うので、その出力には量子化ノイズが多く含まれることになる。このノイズは、ΔΣ変調器内部の後段の回路によって高周波領域に追いやられる(ノイズシェイピングと呼ばれるこの機能については、次回以降に詳しく説明する)。

ΔΣ変調器の出力は、後段のデジタルフィルタに入力される。その入力は、高周波ノイズを含む高速信号である。この段階で、信号そのものの性質はアナログドメインからデジタルドメインに移ることになる。

デジタルフィルタで行う処理は帯域制限とデシメーション(間引き)の2つだが、ハードウエアとしては1つのフィルタ回路として実装されることが多い。その回路によって、入力信号に含まれる高周波ノイズを低域通過の帯域制限フィルタによって減衰させ、データレートをデシメーションフィルタによって引き下げる。すなわち、デジタルフィルタは、ΔΣ変調器からの高速1ビットデータにフィルタリングとダウンサンプリングを施し、低速の多ビットデータ(本来の分解能のデータ)として出力するのである。

逐次比較型などの方式のA-Dコンバータでは、サンプルレートとして存在するのは本来のサンプリング周波数だけである。それに対し、ΔΣ型A-Dコンバータにはサンプルレートが2種類存在する。1つは、入力サンプルレートで、もう1つは出力サンプルレートだ。入力サンプルレートは、先述したとおり、本来のサンプリング周波数よりも高速で、出力サンプルレートは本来のサンプルレート(データレート)そのものになる。これらの比率がΔΣ型A-Dコンバータにおけるデシメーション比(逆の考え方をすれば、オーバーサンプリング比率)となる。このデシメーション比と有効分解能の間には深い関係がある。

今回は概念的な説明にとどめたが、次回以降、ΔΣ変調器や、デジタルフィルタ、デシメーション比などについて詳しく解説する。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。bonnie@ti.com

Copyright © ITmedia, Inc. All Rights Reserved.

図1 ΔΣ型A-Dコンバータの基本構成 一般に、ΔΣ型A-Dコンバータの基本構成は、ΔΣ変調器とデジタルフィルタ(帯域制限フィルタとデシメーションフィルタ)の2つから成る。

図1 ΔΣ型A-Dコンバータの基本構成 一般に、ΔΣ型A-Dコンバータの基本構成は、ΔΣ変調器とデジタルフィルタ(帯域制限フィルタとデシメーションフィルタ)の2つから成る。