DRAMアクセスの高効率化を図る:マルチメディアSoC設計の要(1/2 ページ)

ホームネットワーク機器向けのSoCでは、統合型メモリーアーキテクチャ(UMA)を採用するケースが増えてきた。このアーキテクチャを利用することにより、低価格なDRAMを使うことができるようになった。その結果として、DRAMインターフェースの性能がシステムの性能を大きく左右することにもなった。本稿では、DRAMを用いたメモリーシステムの効率を高めるための設計について論じる。

背景となる要因

ビデオ処理向けのSoC(System on Chip)の設計者にとって、DRAMへのアクセスを高効率化することが重要な課題となっている。その背景には多くの要因がある。

プロセス技術がますます進歩するに連れ、ICの集積度をより高めることが可能になった。また現在では、低価格化への要求が、高い安定性や高速化への要求に代わって市場を牽引している。そして民生市場においては、HD(高品位)ビデオなど、より広い帯域幅を必要とする規格が採用され、非常に高い転送レートが要求されるようになった。これらの要因のほかに、チップ間(オフチップ)の通信は、オンチップの通信速度よりも遅いという問題もある。こうしたことから、システムの多くの機能を1つのチップに集約したSoCが主流となったわけだが、そのSoCにDRAMを集積すると、デジタル/ロジック回路の速度性能が低下するとともに、コストが増大してしまう。そのため、民生用の機器メーカーの多くは、DRAMを別チップとする設計を採用するようになった。

また、DRAMを別チップにした場合、SoC内部の複数の機能ごとにDRAMを用意していたのでは、外部端子やロジック回路、コストがそれぞれ増加してしまう。そのため、特にマルチメディア機器向けのSoCにおいては、1つのメモリーインターフェースを多くの機能で共有する統合型メモリーアーキテクチャ(UMA:Unified Memory Architecture)を採用する動きが活発になっている。

このUMAを採用した場合、一定の性能レベルを保ちつつ、システムコストを最小化するには、DRAMを効率的に使用することが必須条件となる。例えば、何らかの工夫によって、低速なDRAM、つまり低コストなDRAMを使用したり、DRAMの個数を減らして容量を削減したりすることが可能ならば、コストを抑えつつ、性能を上げることができるであろう。

現在では、SoC設計者のたゆまぬ努力の結果、民生用デジタル機器におけるDRAMのバス使用率は、50%をはるかに超えて80%以上に達しつつある。このバス使用率は、アクセス効率を高めた結果である。

2つのポイント

DRAMのアクセス効率を改善するには、システム全体における複雑な相互作用について検討しなければならない。その中でも特に重要なのは、DRAMを使用する多種多様な機能間で送受信される情報の性質と、DRAMの動作を管理するロジックである。

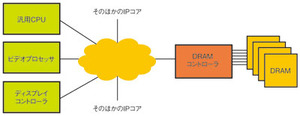

図1は、ビデオ処理機器向けのSoCにおける主要な処理ブロックとDRAMコントローラの接続を示したものである。従来のSoCでは、この接続にはプロセッサを頂点にした階層構造のバスが用いられ、クロックをベースとして機能していた。一方、最新のSoCでは別のシステムによりトラフィックを管理する方法がとられている。そのトポロジとしては、スター構造のクロスバー接続による同期型NoC(Network on Chip)やクロックレスの非同期NoCなどが用いられている。

マルチメディア処理を行う機器、特にHDビデオのデータストリームを取り扱う機器では、高速なバスアクセスと大容量のメモリーを必要とする。そのため、DRAMへのアクセス効率を高めることで、使用するDRAMの個数を削減したり、低速のDRAMを使用したりすることができるならば、低コスト化が図れることになる。つまり、アクセス効率を高くすることが、この用途向けのSoCにとって非常に重要なことなのである。

では、データストリームの処理におけるDRAMのアクセス効率を最大化するためには、どのようなことを検討すべきなのだろうか。以下、検討すべき2つの項目について説明する。

■優先順位

DRAMコントローラは、DRAMへのアクセス要求を発行するIP(Intellectual Property)コアに関する情報をできる限り得る必要がある。しかし、単なるアクセス要求からは、DRAMコントローラがアクセスの優先順位を判断するのに十分な情報を得ることはできない。効率を高めるには、DRAMへのアクセスに付随する情報を明示的にコントローラへと伝達し、処理中の要求と比較して、新しい要求の重要性がどの程度であるのかをコントローラが判断できるようにする必要がある。

旧式のバスでは、要求の中に要求元を識別するための情報が含まれていなかった。従って、DRAMコントローラは何らかの手段によって要求元を推測する必要があった。例えばAHB(Advanced High-Performance Bus)ベースのシステムでは、コントローラは複数のAHBによって、個々の要求に対して適切に重み付けする。このような複数階層のバスシステムでは、DRAMの効率を最大化しつつ、システムの要求も満たすために、DRAMコントローラにおいてさまざまなQoS(Quality of Service)アルゴリズムを用いることになる。

OCP(Open Core Protocol)やAXI(Advanced Extensible Interface)などのより新しいプロトコルでは、要求パケットのさまざまなフィールドに要求元を特定するための情報を付加することができる。

また、OCPのタグやAXIの識別子を用いて、要求元の具体的なタスクを特定できる可能性もある。タグがあれば、インターコネクト(相互接続)による通信とそのターゲット(命令の受信側)は、書き込み順序を維持しつつ、単一スレッド内の競合しないメモリーアドレスへのアクセス順序を変更することができるだろう。

さらに、タグ付きトランザクションは、高度なCPUアーキテクチャにおいても有効である。つまり、DRAMへのアクセス効率を最大化するには、要求元とDRAMコントローラとの間でアクセス要求に関するすべての情報を伝送する必要があるのだ。

■スケジューリング

最新のDRAMコントローラでは、システム内の複数のイニシエータ(命令の発行側)からの要求を保持するコマンドキューを利用できる。同コントローラができる限り柔軟に、コマンド列やそのほかの重要な情報を選択できるようにするには、常に複数の要求を保持しているコマンドキューに対し、最良のスケジューリングを決定できる状態にしなければならない。従って、オンチップのネットワークには、すべての要求を、その要求に関するありとあらゆる情報とともにできる限り迅速に伝送するべきである。これを妨げるような障害があってはならない。

システムのトラフィックを管理する1つの方法は、DRAMコントローラにトラフィックシェーピングやトラフィックオーダリングなどの機能を実現するロジックを加えることだ。DRAMの現在の状態や、ほかのシステム機能からの保留中の要求を把握しているのはDRAMコントローラのみである。そのため、要求のスケジューリングはDRAMコントローラが実施することになる。

仮にDRAMコントローラ以外の部分で、要求の順序を変えたり、調整のためのスケジューリングを行ったりすると、かえってアクセス処理を混乱させることになるだろう。例えば、先に受信したが優先度は高くないと判断した要求は、何らかのストレージ容量を浪費して蓄えられることになる。しかし、優先度が高いとシステムが判断すれば、その要求はスケジューリングを乱すことになり、DRAMへのアクセス効率が低下する。このバランスをとることができるのは、DRAMコントローラだけだ。

より良い方法は、DRAMコントローラが処理可能な大きさの要求を送信すること、その要求はできる限り何らかの情報を削除したものでないこと、1カ所で集中管理的にDRAMの状態とシステムの要求との間の優先順位の決断を行うことなどである。そのほかの方法では、情報の損失やシステムによる誤判断の可能性があり、DRAMへのアクセス効率を低下させてしまうだろう。

システムによっては、インターコネクトにおいて要求の性質が変化してしまうことがある。例えば、インターコネクトにおける遅延によってスケジューリングのタイミングに間に合わない要求を伝送してしまうケースや、時間多重システムにおける割り当てアルゴリズムによって大容量転送が少量転送の列に分割されるケースなどがそれに当たる。

もし、DRAMコントローラがサイズの小さい1つのデータ転送を処理している間に、同様の要求が後から送られてくることがあらかじめわかっていれば、効率を改善するよう制御することができる。同様の要求が送られてくることが推測できていないなら、DRAMコントローラはバンクを閉じてしまうかもしれないし、読み出し処理を挿入してバスの状態を逆転させてしまうかもしれない。これでは効率は低下してしまう。従って、アクセス要求を再順序付けするスケジューリング機能は必須である。たとえ要求元が1つだけであっても、アクセス効率を改善するためにはこの機能は必要だ。

Copyright © ITmedia, Inc. All Rights Reserved.