安価に実現した自動リセット式電流制限回路:Design Ideas

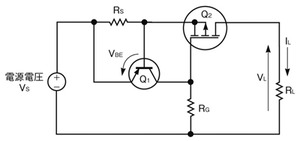

図1の回路は、電流制限回路としてよく知られているものである。この回路では、負荷電流ILの値がほぼVBE/RSに制限される。ここで、VBEはトランジスタQ1のベース‐エミッタ間電圧であり、RSは電源電流の検出抵抗である。通常の動作では、VBEの値が低いのでQ1はオフに保たれ、pチャンネルMOSFETのQ2がゲート抵抗RGを介してバイアスされ完全にオンになる。従って、負荷電流の値は、負荷電圧VLと負荷抵抗RLとだけによって決まる。一方、何らかの要因で負荷電流が増大し、VBEが0.7V近くまで増大すると、Q1が導通し始める。それに伴い、Q2のゲート‐ソース間電圧VGSが低下する。その結果、負荷電流はILMAXIMUM=0.7V/RSの式で決まるほぼ一定のレベルに制限される。

このような線形動作の電流制限回路は、最大負荷電流と電源電圧のいずれか、または両方が比較的小さければ有効に機能する。しかし、この回路は、トランジスタQ2が消費する電力の問題から、適用可能な用途が限られる。例えば、最大負荷電流が200mA、電源電圧VSが24Vである場合、負荷に短絡が生じると、Q2には約5Wの電力が加わる。Q2は、この5Wの電力に適切なマージンを含めた電力を許容できなければならない。また、そのときの接合温度が安全な領域に保持されるようヒートシンクなども必要になる。多くの用途では、このような条件に対応できるようにするには、使用する部品のコストや、サイズ、重量が許容し難いレベルになる。

しかし、この回路に少数の低価格な部品を追加するだけで、過大な電流による消費電力の問題を起こすことなく、効果的に電流制限を行うことができる。本稿では、このようなアプローチによる自動リセット式電流制限回路を紹介する。

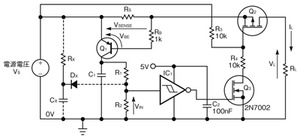

図2の回路では、図1の回路と同様に、トランジスタQ1と検出抵抗RSによって負荷電流ILをモニターする。具体的には、IL×RSに等しい電圧VSENSEが検出される。一方、トランジスタQ2は、図1のQ2とは少し異なる動作となる。Q2は、完全にオンになるか、完全にオフになるかのどちらかで、線形動作の条件は生じない。通常の条件では、Q1のベース電流の量は少なく、ベース抵抗RBによる電圧降下も小さい。そのため、Q1のベース‐エミッタ間電圧は、ほぼ電圧VSENSEに等しくなる。

回路の詳細な動作は次のようになる。まず、負荷電流が少なく、Q1のベース‐エミッタ間電圧が0.7Vより低い通常の状態を考える。この条件ではQ1はオフになり、タイミング調整用コンデンサC1の充電電圧はほぼ0Vである。このとき、シュミットトリガーインバータIC1への入力電圧VINはローレベルになる。その結果、IC1の出力がハイレベル(約5V)になり、この電圧によってトランジスタQ3がオンになる。それにより、Q2のゲートが抵抗R4を介してバイアスされる。このバイアス電圧により、検出抵抗RSとQ2のオン抵抗を介し、電源から負荷に対して電流が流れる。

一方、短絡などの故障によって負荷電流が増大したとする。すると、Q1のベース‐エミッタ間電圧が約0.7Vになり、Q1はオンになる。そしてQ1のコレクタ電流により、C1が急速に充電される。その結果、IC1への入力電圧VINが上昇し、ハイレベルの閾(しきい)値電圧VTUに達する。これにより、IC1の出力がローに変わり、Q3およびQ2がオフになる。結果として負荷電流が0Aまで低下し、Q1のベース‐エミッタ間電圧も0Vになって同トランジスタはオフになる。すると、抵抗R1とR2を経由してC1の電荷が放電し、IC1の入力電圧がローレベルの閾値電圧VTLに達する。その結果、IC1の出力がハイに変わり、Q3とQ2がオンになる。このようにして、電流制限回路が自動的にリセットされる。このプロセスは過大な電流が流れなくなるまで繰り返される。遮断電流値ILMAXIMUMは、図1の電流制限回路と同様に検出抵抗によって決まり、ILMAXIMUM=0.7V/RS〔A〕となる。なお、R1とR2で構成される分圧回路は、IC1の入力電圧が許容値を超えないようにするためのものである。

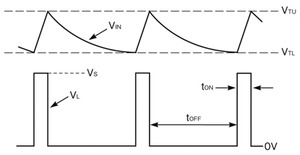

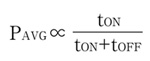

図3は、IC1の入力電圧VINと負荷電圧VLの関係を表している。負荷電流がQ2を経由して流れるのは、Q2がオンの期間だけなので、Q2が消費する電力はデューティサイクルに比例する。つまり、次式が成り立つ。

ここで、PAVGはQ2が消費する平均電力、tONはQ2がオンしている時間、tOFFはQ2がオフしている時間である。C1、R1、R2の値を適切に選択することにより、時定数を十分大きくすれば、Q2がオンしている時間よりもオフしている時間をはるかに大きな値とすることができ、消費電力を抑えられる。なお、各値は、C1の値が過大にならない範囲で、時定数が十分大きくなるよう選定する。

Q1としては、電流増幅度が大きく、最大コレクタ‐エミッタ間電圧が電源電圧よりも大きいものを選択する必要がある。Q2として用いるpチャンネルMOSFETは、バイアス電圧が生じない条件では電源電圧が直接加わることを考慮し、最大ドレイン‐ソース間電圧が電源電圧よりも高いものを選ばなければならない。検出抵抗RSの値は、通常動作時の最大負荷電流が流れる条件で、Q1のベース‐エミッタ間電圧が0.5V以下になるよう選択する。

負荷の種類がフィラメント式の電球や、容量性の負荷、あるいはモーターなどである場合には、突入電流が大きくなる。こうした負荷に対してこの回路を適用すると、電源の投入時に突入電流によってIC1の入力電圧VINが上昇し、リセット機能が誤って働いてしまうことがある。この問題に対処するには、コンデンサCX、ダイオードDX、抵抗RXを追加すればよい。CXは電源投入時には充電されておらず、ダイオードDXを介して印加される電圧VINを0Vの方向に引き下げるよう働く。この動作により、突入電流によるリセット機能の誤動作を防止することができる。

CXとRXの値は、リセット機能が過電流を検出してから正常動作に復帰するまでの時間、言い換えれば、CXの電圧が電源電圧まで上昇してDXが逆バイアスになるまでの時間を決める。この時間は、実験によって検討した結果を基に最適な値とする。その時間を基に、CXとRXの値を決めればよい。検討を行う際の初期値としては、CXを10μF、RXを10MΩといった値にしておくとよいだろう。

Copyright © ITmedia, Inc. All Rights Reserved.