組み込みシステムに適したPCIeのクロック分配技術(2/2 ページ)

ジッターの測定手法

続いて、上述した方法で設計した場合の性能評価について説明する。まずは、PCIeにおけるジッター特性の解析手順から押さえることにしよう。解析手順の規格は、PCIeのジッター規格に関する作業グループPCIe Jitter Working Groupが策定している。同グループは、基準クロックの規定を多くしすぎたり、また少なくしすぎたりしないように留意した。同グループが規定の対象としたのは、送信側PLLのフィルタリング効果、受信側PLLのフィルタリング効果、位相補間器が基準クロックに与える影響、そして、これらPLLのピーキング効果についてである。

作業グループが詳細を規定していない部分は多いのだが、現在のところ、解析手順は大きく4つの段階に分けられる。まず最初に、各サイクルの累積位相誤差を調べる。PCIeのようなシリアル伝送では、累積位相誤差がサイクル間ジッターおよび周期ジッターよりも重要である。ちなみに、パラレル伝送では、累積位相誤差よりもサイクル間ジッターと周期ジッターを重視する。

次に、累積位相誤差に離散的フーリエ変換(DFT)を適用する。これで周波数領域での解析が可能になる。それから、DFT済みのデータをシステム伝達関数に通し、さらに逆DFTをかけて時間領域のデータに戻す。

複素周波数領域におけるPLLシステムのフィルタリング解析は、システムの伝達関数でs=jωとおいて実施する。この等式は連続システムではうまく機能するが、最新のPLLシステムには位相検出器やフィードバック分周器などのデジタル素子が含まれているので、より正確な解析のためにはZ領域でのデジタル解析が適している。ただし、PCIe Jitter Working Groupの検討結果により、S領域解析でも誤差は無視できることがわかった。そこで、S領域による近似モデルを解析に使う。なお、基準周波数がPLL帯域幅の10倍よりも低い場合には、実際の値から大きく乖離してしまうので、PLLの選択には注意が必要である*1)。

ジッター測定における注意点

ジッターの測定に不適切な手法を用いると、測定値は簡単にばらついてしまう。適切な測定手法で得た値の2倍以上になることなど珍しくない。ここでは、ジッター測定におけるいくつかの注意点を紹介する。

まず、被測定物とオシロスコープの接続には、シールド付き同軸ケーブルを使用して、クロック信号をオシロスコープの入力で終端する。高インピーダンスのプローブとしては低容量タイプのものを選び、ワイヤーではなくグラウンドクリップを使って接続する。

また、サンプリング周波数としては、要求仕様に合致したなるべく高い周波数を選ぶ。そして、オシロスコープ画面の垂直軸は分解能を最大にする。電圧測定の精度を高めるためだ。加えて、被測定デバイスには、モニターや電源、携帯電話機などは近付けない。さらに、電源にはできればリニア電源を使用する。差動測定を実施する場合には、2本のケーブルを相互にデスキューする。

実測値の例

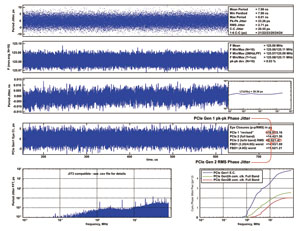

最後に、実測例を示しておく。評価環境としては、米IDT(Integrated Device Technology)社のIC「ICS841S32I」の評価ボードである「ICS8743008I」を2枚用意し、それらをデイジーチェーン接続して試作システムとした。これにより、図5の構成となり、2枚のボードのうち一方がマスター、もう一方がスレーブになる。この状態で、スレーブ側のボードの出力を測定した。測定は、オシロスコープでクロック周期データを取得し、そのデータをジッター解析スクリプトで後処理する方法を採用した。ジッター解析スクリプトでは、周波数領域と時間領域の解析を必要に応じて実施した。

図6に示したのが測定結果である。2.5Gbpsのデータ伝送を解析した結果、位相ジッターは18.91psだった。規定ではピークツーピーク位相ジッターは最大86psなので、4倍ほどのマージンがあることになる。

5Gbpsの伝送では、位相ジッターの最大値がRMS値で定められている。5Gbpsの伝送を解析した結果は、その仕様である3.1ps(RMS値)も満足した。低周波数帯域のジッターは0.52ps、高周波数帯域のジッターは1.47psである(いずれもRMS値)。

PCIeの仕様では、5Gbpsの伝送モードについて、周波数領域における解析用に2つの伝達関数と2つの周波数範囲を規定している。1つ目の伝達関数のポール(極)周波数は5MHzと16MHz、2つ目の伝達関数のポール周波数は8MHzと16MHzである。ジッターの解析対象とする2つの周波数帯域範囲は、低周波帯域が10kHz〜1.5MHz、高周波帯域が1.5MHz〜ナイキスト周波数となっている。ここで「〜ナイキスト周波数」とは、基準クロックの半分の周波数まで解析するということを意味する。例えば、100MHzのクロック周波数では、周波数領域の解析は50MHzまでとなる。ジッター解析スクリプトは、周波数解析を実施する各帯域における2つの伝達関数間の最悪値をリポートするように作成した。

本稿で述べた手法を用いれば、100MHzと125MHzの両クロックをサポートするICを使い、M-LVDS差動対を介してクロックをすべてのボードに分配できる。また、アプリケーションに応じて各ボードをルートのボードまたはスレーブのボード(エンドポイント)のどちらにも割り当てられる。さらに、コンフィギュレーションを実行することで、任意のスロットにボードを配置することが可能である。そして、バックプレーンを通過する基準クロックの周波数を低減することにより、配線レイアウトの制約を緩和し、クロストークを低減することができる。

脚注

※1…"PCIe Reference Clock Requirements," Integrated Device Technology

Copyright © ITmedia, Inc. All Rights Reserved.