「コンパレータ」の選択基準:6つのポイントから最適解を導き出す(2/4 ページ)

POINT 2 : 消費電力/速度

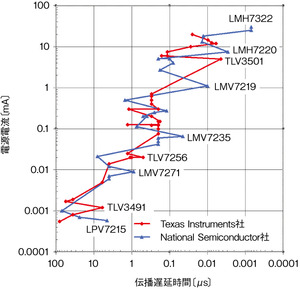

出力方式を決定したら、次に検討するのは消費電力と速度である。現在、半導体メーカーが販売しているコンパレータは、「低消費電力」もしくは「高速」のどちらかを特徴とすることが多い。これは、高速で高精度な部品は消費電力が多く、低速な部品は消費電力が少ないという基本的なトレードオフに基づいている(図2)。例えば、あるメーカーの低消費電力コンパレータは、伝播遅延時間が70μsで、消費電流は1μA未満である。これに対して、米Analog Devices社の「ADCMP572」のような高速コンパレータの伝播遅延時間は150psと短いが、消費電流は44mAと大きい。なお、コンパレータでは、ゲインと速度の間にもトレードオフが存在する。一般に、低消費電力コンパレータはCMOSプロセスで、高速コンパレータはバイポーラプロセスで製造される。

中には、消費電流が少なくて高速の応答が可能な製品も存在する。米National Semiconductor社の「LMV7219」は、伝播遅延時間が7nsで、消費電流は1.1mAと比較的少ない。ただし、ゲインが比較的小さいことが欠点である。なお、一般的に、n型デバイスはp型デバイスより電荷の移動度が高いため、ハイからローへの切り替えのほうがローからハイへの切り替えよりも高速となる。

コンパレータ自身の消費電流に影響を与える要因の1つは、チップ内部の容量負荷である。チップの自己消費電流には、内部の容量に対する充放電電流が含まれるからだ。また、コンパレータを高速にスイッチングさせると、自己消費電流以外に、外部の容量で消費される電流が目立ってくる。コンパレータを高速に動作させるには、容量を急速に充電しなければならず、それにはより大きな電流が必要となるからだ。さらに、動的に動作の状態を変更するモードを備える製品の場合、速度を高めるとともに消費電流も増加する。

アナログ部品のほかの特性と同様に、コンパレータの伝播遅延時間のスペック値も、厳格に定義された条件下においてのみ有効である。例えば、2つの入力端子を駆動する電圧の差により、伝播遅延時間に直接変化が及ぶといった具合である。

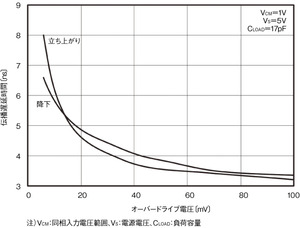

一般的に、オーバードライブが大きいほど伝播遅延時間は短くなる。さまざまなレベルのオーバードライブの下でデバイスが示す伝播遅延時間の範囲のことを「分散(Dispersion)」と呼ぶ(図3)。National Semiconductor社のテクノロジストであるMike Maida氏は、「分散は、半導体テストシステム(ATE)によって高速ロジックチップの伝播遅延時間を測定しようとする場合に重要な仕様となる」と述べる。また、オーバードライブと速度の間に関連性があることから、コンパレータの速度をトグル周波数の関数で表すことに否定的な技術者もいる。有効な遷移であると見なされる出力範囲を定義する必要があり、これは、一般的には、最大出力範囲の10〜90%とされている。

トグル周波数は、伝播遅延時間をできる限り短くするためのオーバードライブに対する要件でもある。Linear Technology社のWhelan氏は、「伝播遅延時間とトグル周波数の間に、必ずしも相関が存在するわけではない」と述べる。同社のコンパレータ「LT1719」と「LT1715」は、どちらも伝播遅延時間は4nsだが、トグル周波数はそれぞれ70MHzと150MHzである。

POINT 3 : ノイズ性能

コンパレータの選定において、検討すべき次の項目はノイズである。しかし、メーカーはコンパレータのノイズに関するスペックを明示しないことが多い。その代わりとして、ランダムジッターのスペックからノイズについて評価することになる。

Analog Devices社のシニア設計エンジニアであるBrian Carey氏は、「デバイスによって増幅されるノイズだけでなく、入力のアパーチャ誤差と出力の立ち上がり/降下時間もジッターに影響を与える可能性がある」と語る。さらに同氏は、「クロック信号用のドライバは、対ノイズ性能の面で最適化された低ゲインのコンパレータであるとも言える」と付け加える。一方、National Semiconductor社のMaida氏は、「CMOS製品の場合、大きな入力トランジスタを使用することにより、フリッカノイズを低減することができるが、この方法では入力容量が増大してしまう」と指摘している。

コンパレータ利用時の注意点

すべてのアナログ回路には、使用時に特に注意が必要になる点がある。コンパレータもその例外ではない。同相入力電圧範囲と発振などが、コンパレータを使って設計を行う上でよく挙げられる問題である。

■同相入力電圧範囲

コンパレータの同相入力電圧範囲は、その製品の入力構造に依存する。そしてコンパレータを使用する際には、入力範囲が電源電圧の範囲から外れないようにしなければならない。そのためには、仕様として入力電圧を制限しておくか、過大な電圧が入力されたらクランプするようにしておけばよい。例えば、LM339の入力端子部にショットキーダイオードを使用するといった具合である。また、コンパレータの入力端子部に備わるESD保護ダイオードは、入力端子の電圧が電源レールより0.6V以上高くならないように入力電圧をクランプしてくれる。

レールツーレールタイプのコンパレータのオフセット電圧と伝播遅延時間は、入力がn型段とp型段の切り替わりのポイントに遷移するときに変化する。コンパレータを利用する際、一般的には、入力端子の一方を固定のDCレベルに設定するため、n型入力段とp型入力段のどちらかだけが機能する状態になる。そのため、遷移は問題にはならない。ただし、重要な例外が1つ存在する。それは、PWM(パルス幅変調)回路でレールツーレールタイプのコンパレータを用いる場合である。この場合、コンパレータの一方の端子に三角波を入力し、他方の端子にPWM信号を入力することが多い。

■発振

コンパレータの出力は、入力の変化が低速であっても高速に変化する。National Semiconductor社のアプリケーションエンジニアであるPaul Grohe氏は、「すべてのコンパレータにはデカップリングの処置を施す必要がある。そうしなければ、回路内の電源とグラウンドに大きな影響が生じる可能性がある。このような影響を考慮し、(ノイズが重畳する可能性のある)電源電圧を分圧したものをコンパレータの基準電圧として用いてはならない」と警告する。

Linear Technology社のアプリケーションエンジニアリングマネジャを務めるTim Regan氏は、「超低消費電力タイプの製品にも、適切なバイパス手段を設ける必要がある。製品の内部に高インピーダンスのノードがあるため、電源電圧変動除去性能はさほど高くない」と述べる。高速のコンパレータは、プリント基板のレイアウトなどからの影響をさらに受けやすい*A)。コンパレータの下にグラウンドプレーンを配置することに加え、浮遊容量の影響で入力部に生じる正のフィードバックによって発振が起こらないようにし、確実に信号の遷移が行われるようにする必要がある。

信号の遷移が確実に行われるようにするための基本的な方法は、コンパレータを用いる回路内にヒステリシス抵抗を導入することである*B)。それによってコンパレータにわずかな正のフィードバックを返すことにより、コンパレータがスイッチングを開始したときに生じるノイズとクロストークを除去する。「ヒステリシス抵抗がなければ、グラウンドから電圧が1mV高くなるだけで発振する」とLinear Technology社の設計部門リーダーであるBrian Hamilton氏は述べる。高速コンパレータの多くは、ヒステリシス抵抗を内蔵しており、ヒステリシス抵抗の値を選択することのできる端子を持つ製品もある。

■ソースインピーダンス

コンパレータを用いる際、もう1つ問題になるのは、大きなソースインピーダンスである。これにより、回路は発振しやすくなり、クロストークや浮遊容量の影響が生じやすくなる。米ON Semiconductor社のアプリケーションエンジニアであるBob Gonzalez氏は、「10kΩの抵抗を入力部に直列に配置してはならない」と忠告する。その抵抗によって、入力へのインピーダンスが増大してしまうからである。デバイスの内部には、必ず寄生容量が存在する。インピーダンスが高いと、その容量の影響により、回路に位相のずれが生じて、発振へとつながってしまう。コンパレータの前に、オペアンプによるバッファ回路や、簡単なエミッタフォロワ回路を使用して、ソースインピーダンスを最小化するとよい。

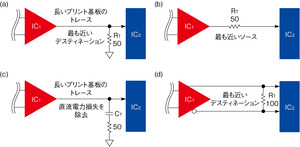

出力を正しく終端することも、コンパレータを用いた設計で生じる問題を防ぐための重要な対応である。コンパレータの出力を長い伝送線に接続する場合、終端しなければ、伝送線の端からの反射が生じる恐れがある(図A)。DC電力を浪費したくない場合には、RC回路を用いたAC終端を検討するとよい。また、伝送先からの反射は生じるものの、その反射を吸収できる直列終端も検討する価値がある。

■温度変化による影響

コンパレータの性能は温度によって変化する。最近では、半導体の設計技術や製造プロセスがかなりの進歩を遂げたこともあり、−40〜125℃の温度範囲で仕様を満たす製品が数多く提供されている。それでも、コンパレータは低温域で発振しやすい。また、高温域ではベース–エミッタ間の電圧が低くなって、ほかの性能値に影響を与えることがある。動作時に生じ得るすべての温度範囲において回路全体を評価する必要がある。National Semiconductor社のMaida氏は、「最大の問題は、伝播遅延時間が温度によって変化することだ。低温になると高速になり、高温になると低速になる傾向にある。同相入力電圧範囲も温度によって少し変化する。一般的に、高温になるとゲインは低下する傾向にあり、これは設計余裕度についての課題となる」と語る。

脚注

※A…Williams, Jim, "High Speed Comparator Techniques," Application Note 13, Linear Technology, April 1985, http://cds.linear.com/docs/Application%20Note/an13.pdf

※B…Mancini, Ron, "Adding hysteresis to comparators," EDN, May 3, 2001, p.22, http://www.edn.com/article/CA84881

Copyright © ITmedia, Inc. All Rights Reserved.