第12回 技術者のための回路設計開発フロー その2「制約条件の設定編」:FPGA Insights

「開発期間の短縮」や「コストダウン」といった、機器設計者が抱える悩みを解決できる手段の1つとして、FPGAの採用が拡大している。これまでFPGAになじみの薄かった設計者にとっても、さまざまな電子機器の設計にFPGAを使いこなしてみる好機が訪れている。本稿では『これさえ知っていればFPGAの設計ができる』という4つの基本ステップを4回にわたって解説する。今回はステップ2となる『制約設定』についてわかりやすく解説する。

ステップ2:制約設定

FPGAの設計では、チップが設計者の期待値通りの動作が実現できるよう、論理合成/配置配線を行う前に、いくつかの制約条件を開発ツールに入力しておく必要がある。設計の手戻りを少なくし、チップの開発期間を短縮し、無駄なチップコスト/開発コストを発生させないためには、制約設定を正しく行うことがとても重要となる。制約を設定するには、開発ツールに付属したウィザードを利用したり、テキストファイルに直接記述してインポートしたりする方法がある。制約設定が正しく行われていれば、最終的に開発ツールが設定された要求を満たすように、チップの回路構成を最適化してくれる。

今回は、制約の中でも代表的な「ピン・アサイン」と「タイミング」の2つの制約を取り上げる。パソコン画面上に表示されるGUI(Graphical User Interface)によって操作性が向上し、初めてFPGAを設計する技術者でも容易に作業が行えるアルテラの設計ツール「Quartus II 」を用いて、その具体的な設定方法などを紹介する。

GUIでピン設定を容易に

ピン・アサイン制約:Pin Planner(ピン・プランナー)

1つ目の制約は、ピン・アサイン制約である。ピン・アサインとは、ハードウエア的に接続されるようFPGAのピン番号と回路図上のピンを正しく対応させることである。ただし、単にピン同士を電気的に接続するだけでは、信号品質(シグナルインテグリティ)やタイミングの問題が実機上で生じることもある。あるいは配線層の増加や再設計により、プリント基板のコストアップ要因になることがある。

プリント基板上でFPGAを正しく動作させるためには、ピンの割り当てを行う際に、プリント基板上の回路設計/電子部品の実装も考慮しなければならない。クロックピンやディファレンシャルピンの配置といったI/Oピンの構造、内部のセル構造などに関連するチップ固有の制約についてはデータシートで確認して、ピン・アサインの制約を正確に行うことが重要となる。

プリント基板上におけるFPGAの配置と、その配線の要件を満たしたピン・アサインを作成することによって、FPGA設計者、プリント基板設計者およびハードウエア設計者の間で発生する手戻りをできる限り少なくすることができる。それが結果的に設計のコスト削減や期間短縮につながることとなる。

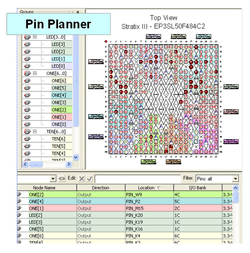

Quartus II ではピン情報の編集を行うために可視化ツール「Pin Planner(ピン・プランナ)」が搭載されている。この機能を使用し、作成した回路(デザイン)の入力ピン、出力ピンおよび双方向ピンを FPGA の目的のピンに割り当てることができる(図1)。このPin PlannerはGUIを使用して、ドラッグ&ドロップなどグラフィカルにピンの設定が行える。このため、Quartus II を初めて使用する設計者でも比較的容易に操作できる点が特徴だ。また、Pin Plannerではピンの割り当てだけではなく、ピンのI/O規格の設定や未使用ピンの処理方法なども設定することができる。

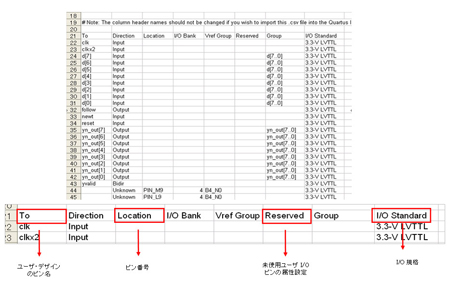

Quartus II ではGUIでの操作に加えて、CSV(カンマ区切り)ファイルを使用した設定も可能である。CSVファイルを編集する際の表記については、決められたフォーマットで記述する必要がある。決められたフォーマットと言っても、特に難しいフォーマットを使用するわけではない。フォーマットの例を図2に示す。

CSVファイルにおいて、必要な項目のみ情報を編集する。それ以外は空欄にしておく。その一例を以下に紹介する。

■ピン番号を変更する場合は、Location欄のピン番号を編集する。記述は以下のようになる。

記述 : PIN_番号 記述例 : PIN_E2

■I/O規格を変更する場合は、I/O Standard欄の規格名を編集する。記述は以下の通り。

記述例 : 3.3V LVTTL

上記のように、Quartus II を用いてピン・アサイン制約を設定する方法としては、GUIベースの “Pin Planner”と、“CSV”ベースの2つのインポート方法が用意されている。このため、設計者は使用するチップの種類や作業効率、設計の熟練度などに応じて、設定しやすい方法でピン・アサインを行うことができる。

SDCの作成/編集も簡単操作

タイミング制約:TimeQuest(タイム・クエスト)

2つ目の制約は、タイミング制約である。チップ内外でクロック周波数や入出力のタイミングがマッチしないと、チップやシステムレベルで不具合を引き起こしたり、十分な演算性能が得られなかったりする可能性がある。

チップ内部や入出力の回路が複雑になればなるほど、タイミング制約の設定もより複雑となる。また、プロセスの微細化が進展したことで、これまで以上にタイミングのばらつきが生じやすくなるなど、タイミング設計に影響を与える要因が増えている。一方で、タイミングの制約を過度に厳しくすると、設計完了(タイミング収束)までの時間がかかりすぎて、設計終了が遅れるという問題も出てくる。

このような状況に陥らないようにするために設計者は、開発ツールに対してタイミングに関する設計要求を指示(設定)する必要がある。基本的なタイミング制約の例としては、クロック周波数の指定がある。複数のクロックが1つのチップ内に混在する場合には、それらの関係を制約として定義することが必要となる。

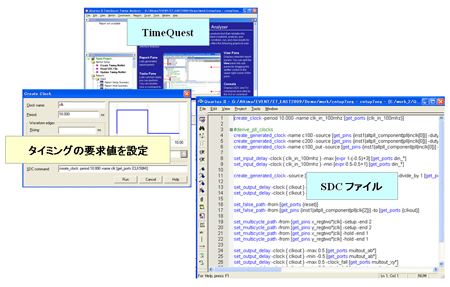

Quartus II に搭載されているタイミング検証ツール「TimeQuest」を使って、FPGA内部の周波数や I/Oタイミングなど、設計者が期待するタイミング値を設定することができる。Quartus II に標準搭載されたTimeQuestは、ASIC業界では標準の制約手法となっている「Synopsys Design Constraints (SDC)」 を採用したハイエンドな解析エンジンである。

TimeQuest では、Quartus II のテキスト・エディタを使用しSDCの作成/編集を行う。一般的にSDCの作成/編集を行う場合は、設計者が直接コマンドを入力して制約を設定するが、TimeQuest のエディタはGUIを使用して制約のコマンドを入力することもできるため、設計者がコマンドを覚えていなくても済むなど、簡単操作が特徴である(図3)。このため、コマンド入力によるSDC作成に対して「経験や知識がまったくない」、あるいは「経験や知識は少しあるが十分ではない」といった不安を抱える技術者でも容易にSDCを作成することが可能である。既存のSDCファイルの内容を取り込むことも可能だ。

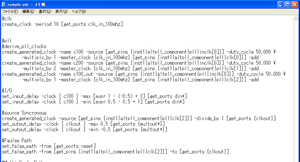

SDCファイルを作成/編集する作業は、図4のように一般的なテキスト・エディタでも行うことは可能だが、通常のテキスト・エディタにはSDCシンタックスのカラーリング機能がサポートされていない。このため、設計者はコマンドを直接記述する場合には誤記に注意する必要がある。初心者の方にはSDCシンタックスのカラーリング機能がサポートされているQuartus II のテキスト・エディタを使用して、作業されることをお勧めする。

このように、Quartus II で行う制約設定には、GUI 対応のほかに直接制約内容を入力またはインポートする方法が用意されている。これにより、FPGAの設計者は初心者から熟練者まで、状況に応じて好みの方法を選択することができる。

上述したデザイン入力方法に基づいてFPGAの論理回路設計を行えば、設計者が期待する設計仕様を容易に実現していくことが可能となる。論理回路の設計が完了したあとに、その回路が期待した動作をするかどうかを確認するために 「ファンクション・シミュレーション」 を行う。もし、期待値通りの動作にならなければ、記述を修正したりバグを取り除いたりする作業を行って設計が完了する。

制約設定が完了した後は、コンパイル(論理合成および配置配線)を実行する工程となる。コンパイル含むそれ以降の作業については、次回(ステップ3)でわかりやすく紹介する。

公開中(2010年4月〜2010年12月掲載分)

第9回 トランシーバを内蔵した低コストFPGAの活用法(前編)

第10回 トランシーバを内蔵した低コストFPGAの活用法(後編)

第15回 DDR2 の実装からデバック手法:〜ステップ1 FPGA を用いた DDR2 SDRAMインタフェース〜

第16回 DDR2 の実装からデバッグ手法:〜ステップ2 DDR2 FPGA デザイン設計〜

第17回 DDR2 の実装からデバッグ手法:〜ステップ3 FPGA のデバッグ手法『SignalTap II Logic Analyzer』〜

第18回 DDR2 の実装からデバッグ手法:〜ステップ4 FPGA のデバッグ手法『Debug GUI』〜

第19回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(前編)

第20回 FPGAで実現する 産業用ワイヤレスセンサーネットワーク(後編)

第21回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(前編)

第22回 産業機器におけるTCO ―FPGAで回路設計の発想を転換する(後編)

第23回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ1:USB3.0の概要〜

第24回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ2:FPGAを用いたUSB3.0の基板設計〜

第25回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ3:USB3.0 Boardのベンチマーク測定〜

第26回 低コストFPGAで実現するUSB3.0インタフェース 〜ステップ4:USB3.0 Boardのリンク検証事例〜

関連情報

●TimeQuest タイミング・アナライザ: FPGA 設計におけるSDC のネイティブ・サポート

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2014年3月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。