ポリフェーズフィルタの基本を知る:FIRフィルタの効率的な実装手法 (3/3 ページ)

ポリフェーズフィルタの活用

上述した問題を回避してFIRフィルタを実現する手法が、本稿で紹介するポリフェーズフィルタである。ポリフェーズフィルタの基本的な概念は、FIRフィルタをいくつかの小さな要素に分割し、それらの要素から得られた結果を組み合わせることで、必要なフィルタ処理を実現するというものだ。ここでは、間引き処理、補間処理の順に、ポリフェーズフィルタの基本的な構成と、そのメリットについて説明する。

■間引き処理

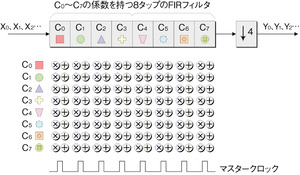

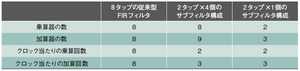

図11に示したのは、間引き処理を行う8タップの従来型FIRフィルタを記号で表現したものである。間引き係数は4で、周波数Fのマスタークロックで動作するとしよう。ここまでに説明したように、フィルタリングの後に不要なサンプルを捨てるわけだが、この方法では、最大周波数であるマスタークロックでフィルタリングを行うので効率が良くない。つまり、各タップはマスタークロックのすべてのタイミングで、乗算と加算を実行することになる。

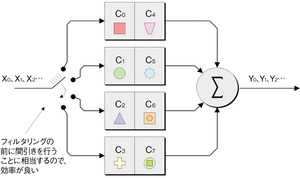

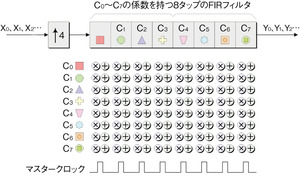

これに対し、ポリフェーズフィルタでは、元の8タップのFIRフィルタをいくつかに分割するようにして構成する。例えば、図12のように、2タップのサブフィルタを4つ使うといった具合である。このフィルタは、先ほどと同じ周波数Fのマスタークロックで動作し、サンプルは“回転スイッチ(Rotating Switch)”にデータストリームとして供給されるものとする。この回転スイッチは、標準的なロジック手法によって実装する。1つ目のサンプルX0は1つ目(図のいちばん上)のサブフィルタに、2つ目のサンプルX1は2つ目のサブフィルタに、3つ目のサンプルX2は3つ目のサブフィルタに、4つ目のサンプルX3は4つ目のサブフィルタに入力する。その後は、5つ目のサンプルX4を1つ目のサブフィルタに、6つ目のサンプルX5を2つ目のサブフィルタにという具合に回転スイッチで振り分けていく。

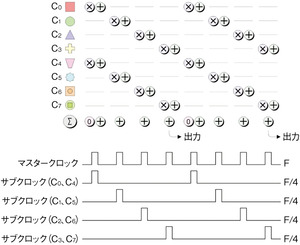

このようにしてサブフィルタに分割すると、飽和/オーバーフローの可能性を低減できる。通常は、最後の加算処理についてのみ、飽和/オーバーフローの考慮を行えばよい。また、サブフィルタを使用すると、実質的にはフィルタリングの前にデータを間引きすることになる。そのため、直接的に効率の向上につながる。また、4つのサブフィルタは、F/4の周波数で動作させれば済むことになる(図13)。

シンプルな考え方で構成した8タップの従来型FIRフィルタでは、各タップにレジスタや汎用ロジックに加えて乗算器と加算器を設けなければならない。つまり、乗算器と加算器は8個ずつ必要になる。フィルタの後段には、不要なサンプルを捨てるためのロジックも必要だ。

同様に、上で示した2タップ×4個のポリフェーズフィルタの各タップにも乗算器と加算器があり、乗算器と加算器は計8個ずつとなる。ポリフェーズフィルタにおいて、フィルタの前の回転スイッチに必要なロジックの量は、8タップの従来型FIRフィルタにおいて、不要なサンプルを捨てるためのロジックとほぼ同量で済む。それ以外には、4つのサブフィルタからの結果を蓄積するためのロジックと1個の加算器が必要となる。従って、このポリフェーズフィルタには、8タップの従来型FIRフィルタよりも少し多くのロジックが必要だということになる。

しかし、8タップの従来型FIRフィルタは、マスタークロックのすべてのタイミングで8回の乗算と8回の加算を実行しなければならない。一方、ポリフェーズフィルタでは、マスタークロックの各タイミングに動作するのは、1つのサブフィルタだけである。この例では、各サブフィルタは2タップなので、各タイミングで実行されるのは、2回の乗算と2回の加算のみとなる。

4つのサブフィルタによる処理結果を積算する部分でも、マスタークロックの各タイミングで1回の加算を行う。4クロックサイクルの1サイクル目には、この積算器を0にクリアする処理も行われる。積算器は、4つのサブフィルタの結果を合算し、4クロックサイクルの4サイクル目に新しい値を出力する。このポリフェーズフィルタの各サブフィルタは、実質的に、8タップの従来型FIRフィルタの1/4の周波数で動作する。つまり、各クロックタイミングにおいて、積算部での加算を入れて、2回の乗算と3回の加算のみを行うことになる。そのため、8タップの従来型FIRフィルタに比べて、かなりの消費電力を節減することができる。

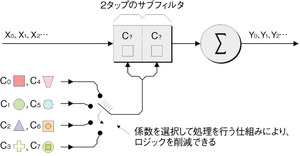

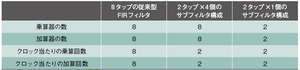

また、このポリフェーズフィルタの4つのサブフィルタは、8タップの従来型FIRフィルタと比較すると、それぞれ1/4の時間しか使用されない。そのため、実際には図12より、もう少し洗練された実装が可能である。図14に示したのは、2タップのサブフィルタを1個だけ使用するように改善したものだ。各タップには乗算器と加算器を設け、各クロックタイミングで適切な2つの係数を選択して使用する仕組みだ。各タップには、演算のコンテキストを維持するためのレジスタとロジックも必要になるが、図12のポリフェーズフィルタからさらに乗算器と加算器の数が減少することを考えれば、この分の追加はまったく問題にならない。このポリフェーズフィルタでも、各クロックタイミングで実行するのは、2回の乗算と3回の加算のみである(表1)。

■補間処理

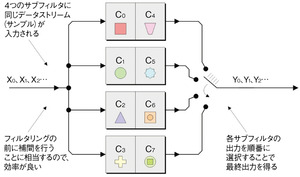

続いて、補間処理について示す。まず、図15に、8タップの従来型FIRフィルタによる補間処理の記号表現を示す。この例では、アップサンプリング(値が0のサンプルを挿入する処理)は、フィルタリングの前に行われるものとする。

次に、8タップのFIRフィルタを2タップ×4個のサブフィルタに分割したポリフェーズフィルタを考える(図16)。この場合、同じ入力データストリーム(サンプル)が4つすべてのサブフィルタに供給され、4つのサブフィルタからの出力を1つずつ順番に選択することにより、出力データストリームが得られる。このポリフェーズフィルタの乗算器と加算器の数は、8タップの従来型FIRフィルタと同じである。しかし、実質的には補間前にフィルタリングすることになるため、サブフィルタはマスタークロックの1/4の周波数で動作すればよく、消費電力が大きく削減される。また、このように構成したポリフェーズフィルタには、アップサンプリング用のロジックが不要である。

さらに、図14と同様の手法で係数を取り扱うことによって、元のポリフェーズフィルタを、2タップのサブフィルタ1個で置き換えることが可能である。それにより、乗算器と加算器の数を削減することもできる(表2)。

Copyright © ITmedia, Inc. All Rights Reserved.