デジタル制御電源を学ぶ(2) デジタル制御用ICの特徴を理解しよう:Design Hands-on(2/3 ページ)

デジタルは制御回路の集約に向く

次に、アナログ制御方式とデジタル制御方式の回路構成の違いについて見てみよう。制御回路を構成する要素や信号処理の流れには、どのような違いがあるのだろうか。

まずはアナログ制御方式だ。出力電圧の大きさをアナログ信号(連続振幅・連続時間信号)のまま検出し、アナログ回路(オペアンプ、コンパレータ)と受動素子(抵抗、コンデンサ)を組み合わせたアナログ信号処理(アナログフィルタ)を経て制御量を導出する。そして、アナログPWM波形生成器によってアナログPWM駆動波形(連続振幅・離散時間信号)に変換するという流れだ。このようにアナログ制御では、計測から制御量の導出までを一貫して連続時間信号で扱うため、複数のスイッチング電源を制御する場合には制御回路を個々に独立した回路として実現せざるを得ない。また計測から制御量の導出までに要する時間は、アナログフィルタ特性に起因する遅延時間を無視すれば、オペアンプとコンパレータを組み合わせて構成したアナログ回路の遅延時間に相当し、それでスイッチング周期の下限(スイッチング周波数の上限)が決まる。

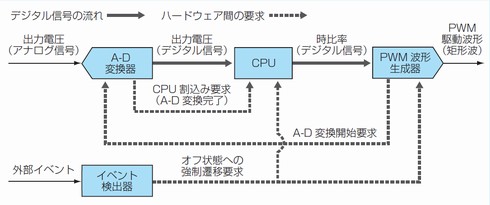

一方、デジタル制御方式はどうだろう。A-D変換器によってデジタル信号(離散振幅・離散時間信号)に変換した数値データからCPUのデジタル信号処理(デジタルフィルタ)を経て制御量を導出する。そしてデジタルPWM波形生成器によってデジタルPWM駆動波形(離散振幅・離散時間信号)に変換するという順番だ(図3)。

先ほどのアナログ制御方式では、一連の信号処理を担う回路の構成要素すべてを常時稼働させておかなければならなかったが、デジタル制御方式ではその必要が無い。A-D変換器がある特定のタイミングでアナログ信号を数値データに変換した後は、制御量を導出するCPUも、制御量が示すタイミングにPWM駆動波形の状態を遷移させるデジタルPWM波形生成器も、それぞれの入力は、動的な(時間とともに変化する)アナログ信号ではなく、静的な(時間をおいても変化しない)数値データになるからだ。従って、A-D変換器やCPUは必要に応じて稼働させればよく、常時稼働させなくてもかまわない。

また、計測から制御量の導出までに要する遅延時間は、デジタルフィルタ特性に起因する遅延時間を無視すれば、A-D変換器の変換時間とCPUの信号処理時間の合算になり、それでスイッチング周期の下限が決まる。デジタル制御ICとして新日本無線の電源制御向用DSC「NJU20011」を例にとると、信号処理周期とスイッチング周期を同じとした場合、遅延時間はおよそ1μsである。

以上より、デジタル制御方式は制御回路を集約しやすい回路構成であり、アナログ制御方式はスイッチング周波数を高くしやすい回路構成であるといえる。

制御回路内では自動で連動

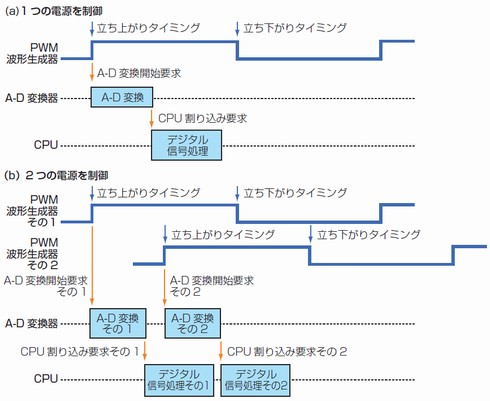

図4(a)は、デジタル制御方式のスイッチング電源において、A-D変換器による出力電圧の計測とCPUによる信号処理がPWM波形生成器と連動する過程を時系列で示している。先ほど示した図3と併せて見てほしい。

PWM波形生成器は基準クロック周波数でインクリメントするカウンタで構成され、ソフトウェアで設定された比較値との一致検出を基本動作とする。ソフトウェアで設定可能な比較値はPWM波形生成器ごとに複数あり、一致検出した結果(タイミング)をPWM駆動波形の論理レベルの高/低の切り替えに適用するだけでなく、A-D変換器の変換開始トリガーに適用することも可能だ。

また、A-D変換器はこの変換開始要求をトリガーとしてそのタイミングのアナログ信号を数値データであるデジタル信号に変換し、変換完了時は割り込み要求としてCPUに通知する。その割り込み要求を受けたCPUはデジタル信号処理ソフトウェアを実行し、次の制御量として比較値を更新する。

このように一巡するハードウェアの連動は、それぞれのハードウェアをソフトウェアで初期設定すれば自動で実行される。ソフトウェアで処理することが減るので、スイッチング周期のうちCPUが稼働してソフトウェアを実行する期間は短くなる。

ここまでは、1つのスイッチング電源を制御する過程を見てきたが、1つのA-D変換器と1つのCPUを搭載する制御ICが複数のスイッチング電源を制御する場合はどうだろう。図4(b)に、2つの電源を制御する場合を例示した。個々の電源に着目すれば、ハードウェアが連動する過程は1つの場合と同じである。

ここで注目すべきは、A-D変換器とCPUが要求に応じて順序よく稼働している点だ。この図から、複数の電源を1つの制御ICで制御可能かどうかを判断する基準が読み取れる。すなわち、A-D変換開始要求から比較値の更新までに要する時間が各々の電源についてスイッチング周期内におさまれば制御可能であり、別の見方をすれば複数の電源制御に要するA-D変換器の総稼働時間およびCPUの総稼働時間がスイッチング周期内におさまれば制御可能である。

スイッチングノイズの影響を抑える

A-D変換器の変換結果と実際の値に誤差があっても、それが定常的な誤差であれば、変換結果を補正することで取り除ける。例えば12ビット分解能のA-D変換器なら、1/4096の細かさで補正することが可能だ(4096は212)。

しかし、スイッチングノイズのように非定常的な誤差はこの方法では補正できないので、PWM波形生成器に連動してA-D変換を開始する仕組みを利用して、ノイズが発生する期間を回避する。そもそもノイズの発生要因はオン状態とオフ状態を遷移させるスイッチング動作にあり、その遷移タイミングを操作しているPWM波形生成器からの信号でA-D変換器の稼働タイミングを操作するのは理にかなっている。

ただ、スイッチング動作に起因しない突発的なノイズへの対策も必要だ。例えば、A-D変換を複数回実行した結果にフィルタ処理(平均化など)を施したり、変換結果そのものに制限を掛けて過剰に反応させない手法も有効である。

もう1つ、ノイズ発生源からの対策を見てみよう。同じスイッチング周期を持つ複数のPWM駆動波形を同期させるとスイッチングのタイミングが重なってしまいスイッチングノイズの量が増えて変換誤差への影響が大きくなることは想像できる。そこで反対に、各PWM駆動波形に意図的に位相差を設ければ、スイッチングのタイミングを分散させることができ、その影響を抑えることが可能になる。

これらは、デジタル制御ICならではの手法だといえる。全ての事象が発生するタイミングを管理して、ハードウェアを制御できるからだ。

Copyright © ITmedia, Inc. All Rights Reserved.