計測面からのぞくSerial ATAの高速化技術:高速シリアル・インターフェイス入門(3)(1/2 ページ)

今回は、純粋なシリアル・インターフェイスであるSerial ATA(SATA)を取り上げます。パソコン内部のハードディスクの配線を簡素化/高速化するために、ATAをシリアルに置き換えることが目的だったSATAは、その用途が拡張しています。

第3回となる今回は、純粋なシリアル・インターフェイスであるSerial ATA(SATA)を取り上げます。図1は、本連載の第1回「なぜいま、高速シリアル・インターフェイスなのか」でも紹介したパラレス・インターフェイスのUltra ATA対応ハードディスクと、SATA対応ハードディスクを並べたものです。

本来のSATAの目的は、パソコン内部のハードディスクの配線を簡素化し、高速化するためにパラレル・インターフェイスであるATAをシリアルに置き換えることでした。しかし、現在はeSATAと呼ばれる外部ハードディスクとの接続にも用いられるなど、用途が拡張されています。

SATAの概要

SATAは、2003年1月7日付けでSerial ATA:High Speed Serialized AT Attachment Revision1.0aとしてリリースされました。データ転送速度は1.5Gbpsで、8b/10b変換(注)を利用しているため、転送速度は150Mbytes/sです。計画段階ではパラレル・インターフェイスUltra ATA100(転送速度:100Mbytes/s)の1.5倍でしたが、最終的にUltra ATAが120Mbytes/sまで高速化したことで、速度優位性は1.25倍と計画よりも小さくなりました。

しかしながら、7ピンのコネクタと大幅な配線量の削減が行われています。また、転送速度は、2004年5月26日にSerial ATA II: Electrical Specification Revision 1.0がリリースされて2倍の3Gbpsとなり、2009年5月27日付でSerial ATA Revision 3.0がリリースされ、さらに2倍の6Gbpsまで速度の向上が図られています。このように基本的なアーキテクチャを継承しながら、高速化/高機能化が進められる規格をスケーラブルと呼びますが、Serial ATAに限らず、ほとんどのシリアル・インターフェイスはスケーラビリティを持っています。

8b/10b変換

意外と誤解しているエンジニアが多いのがPLLです。PLLはPhase Lock Loopの略なので文字通り位相を基準にロック動作が行われますが、周波数シンセサイザの応用のイメージが強いので、周波数でロック動作が行われると勘違いしてしまうようです。位相さえ合っていればハーモニック・ロックと呼ばれる現象ですが、周波数が2倍だったり3分の1だったりしてもロックします。

つまり、一定期間内にロック動作を行わないと、クロックの周波数がずれてしまった状態でロックしてしまう可能性が出てしまいます。クロック動作をするためには位相の比較をしなければなりませんが、位相の比較を行うには位相検出の基準となるエッジがデータ信号に存在しなければなりません。ここに挙げたSATAなどを含めて、一般的なシリアル・インターフェイスではNRZ(Non-Return to Zero)が使われているので、エッジはデータが0から1または1から0に変化するときに現れます。

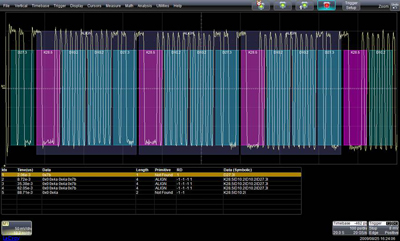

つまりFFのようなデータが続いたりすると、エッジはまったく現れません。これでは、上記のように期待されるPLLの動作が保証されません。そこで、8ビットのデータを適度にエッジを含む10ビットのコードに変換することで、FFのようなデータを送信しても1010110001のようなコードに変換されるため、エッジがコードの中に存在し、PLLの動作を保証することができます。8b/10bエンコードにはそのほかにも、0と1の数を同じにしてDCレベルの変動を抑えることをも目的としています。下図は取り込んだSATAの信号をオシロスコープ上で8b/10bデコードを行い、波形上に対応するコード名を表示しています。

高速化を支える技術

ここでは第1回で示した高速伝送を支える技術のキーワードに従って解説をしていくことにしますが、同時に信号計測における技術的課題と対策についても説明していきたいと思います。

・LVDS

第1回で高速化に有効な手法として低振幅を上げましたが、SATA Gen1では、差動信号の振幅で±500mVと規定されています。立ち上がり時間(20〜80%)は、Gen1の1.5Gbpsでは最短で100ps、Gen2の3Gbpsでは最短で67ps、Gen3の6Gbpsでは最短で33psと規定されています。

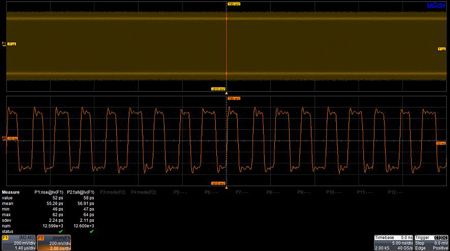

振幅信号に対しては、お約束事のように差動伝送が用いられます。図2はSATAの信号を示していますが、ここで示した波形はGen3の6Gbpsの信号です。実際の立ち上がり時間は平均で55.26psになっていますが、規格では下限が33ps、上限が68psとなっていますので、この信号は合格となります。

・CRU(Clock Recovery Unit)

前回「あらためて学ぶ、DDR2の高速化技術」で紹介したDDR2は、クロックがデータと別に供給されていましたが、SATAではデータを送る信号線だけでクロックを送る信号線が存在しません。クロックはデータ信号に埋め込まれており、レシーバでこのデータ信号から埋め込まれたクロックを再生するCRUがあります。このCRUの性能によって通信品質が大きく左右されることは、第1回のCRUの説明部分で紹介したとおりです。

SATAの場合には、CRUの特性が規格として規定されるようになったのはSATA IIからです(現在はSATA IIという呼び方ではなく、SATA Gen1、SATA Gen2のように呼称します)。しかし、規格で規定されるCRUは送信器信号評価用に規定されたもので、実際のICに組み込まれているCRUは、各社それぞれ自由に設計していいことになっています。内部接続のSATA Gen2では、2次のPLLで、ダンピング・ファクターが0.7070〜1まで、帯域が300MHzと6MHzの2種類が規定されています。

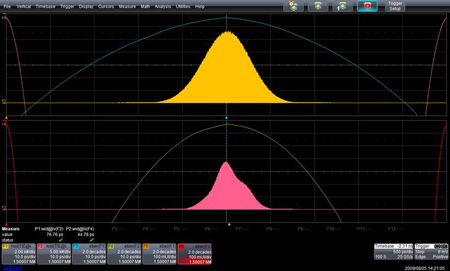

帯域が2種類あるのは、SSC(スペクトラム拡散クロック)が想定されているからです。帯域内のタイミング変動にはPLLが追随できるので、データ信号の揺れを相殺することが可能です。ここでは、HFTP(後述)というテストパターンを用いたジッタの測定で6MHzの帯域のPLLを用いると、SSCと、低周波の揺れを相殺することができます(図3の上)が、300MHzの帯域のPLLを用いると、より高い周波数の揺れまでも相殺することができます(図3の下)ので、計測されるジッタ量は小さく見えます。

・OOB(Out-Of Band)

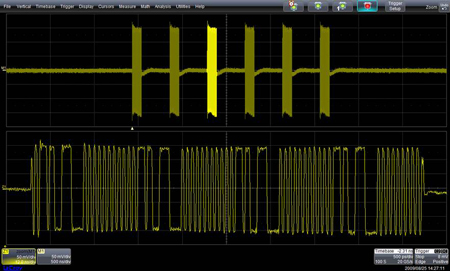

SATAの通信を始める前には、図4に示したOOBと呼ばれる特殊な信号をやりとりし、リンクを確立します。OOBにはCOMINIT、COMORESET、COMWAIKの3種類がありますが、リンクの確立には、最も遅い伝送速度である1.5Gbpsで使われます。リンクが確立されると、伝送速度が複数存在するのでネゴシエーションと呼ばれる操作で、3Gbps、6Gbpsと上げながら、可能な限り高速の伝送速度に設定をして通信が始まります。これはドライブの挿抜を行った場合にも、ホストとドライブが同期をして適切な伝送速度で通信が行えるようにする工夫です。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 Ultra ATA対応HDDとSerial ATA対応HDD

図1 Ultra ATA対応HDDとSerial ATA対応HDD 8b/10bデコードの例

8b/10bデコードの例 図2 SATA Gen3の信号

図2 SATA Gen3の信号 図3 SATA Gen2 HFTP信号のジッタ計測

図3 SATA Gen2 HFTP信号のジッタ計測 図4 SATAのOOB信号(COMINIT)

図4 SATAのOOB信号(COMINIT)