低振幅・低周波のセンサー出力を扱う、アナログ信号調節の最新テクニック:アナログ設計(3/5 ページ)

計装アンプを独自に設計する

Touchstone Semiconductorでマーケティングアプリケーション部門のバイスプレジデントを務めるAdolfo A Garcia氏は、電源電圧が3V以下と低くなってきたことで計装アンプの選択肢が狭くなっていると指摘する。そこで、オペアンプの入出力特性やDC特性を理解し、回路トポロジに明るい設計者は、独自に計装アンプを設計するようになるだろうと同氏は述べる。

2個のオペアンプを使った計装アンプ回路と、3個のオペアンプを使った計装アンプ回路は、ごく一般的な計装アンプを実現する。それぞれについてもう少し詳しく説明しよう。

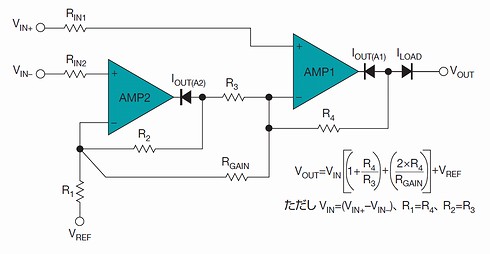

2個のオペアンプを使った計装アンプの回路図を図4に示す。単電源でレールツーレールの低消費オペアンプを選択する場合、基本的にはDC特性とAC特性を検討することになる。DC特性にはVOS、TCVOS、AVOL(MIN)、IOS、VOH(MIN)およびVOL(MAX)が含まれる。AC特性には入力換算雑音や帯域幅などが入る。

用途にかかわらず、出力ダイナミックレンジを最大化することが回路性能の最大化を実現するための鍵になる。Garcia氏によると最も良い選択肢は、出力段ダイナミックレンジが最も広い単電源アンプである。これは出力段の飽和をなるべく避けるためだ。

図4中に示した回路伝達関数に含まれる、基準電圧(VREF)に注目しよう。回路図中のアンプAMP1の出力の飽和を避けるには、計測アンプ出力信号はVREFを基準に評価しなければならない。電源電圧が3V以下の回路では、ダイナミックレンジを最大化するとともに出力段の飽和を防ぐには、「単純にVREFを電源電圧の1/2に設定するだけで十分だ」と結論することもできそうだ。Garcia氏によると、この結論が妥当なのは、選択したオペアンプのVOH(MIN)とVOL(MAX)の仕様値が電源基準レベルに対して対称的な場合だけである。

差動入力信号電圧(VIN)、入力コモンモード電圧(VCM)、基準電圧(VREF)を備えた計装アンプ回路では、VREFがAMP1の出力電圧振幅の中央(電源電圧の半分ではない)になるようにバイアスすることが望ましい。これを式(1)に示す。

VREF = (VOH(MIN)+VOL(MAX))÷2 ―――― 式(1)

計装アンプの利得は、出力段が飽和しない範囲で選択する。2個のオペアンプで実現される計装アンプの回路ゲインは式(2)で求められる。

回路利得 = (VOH(MIN)+VOL(MAX))÷(2×VIN(MAX)) ―――― 式(2)

なお、式(2)で、VIN(MAX)は計装アンプ回路への差動入力の最大値を意味する。回路利得が決まると、回路出力を飽和させずに入力できる差動電圧の最大値が求められる。

動作時の消費電力を最小化するには、抵抗器の値は100kΩ以上としておく。そしてノイズと帯域幅を考慮して、最適な値を選択することになる。ここで重要なのは、オペアンプのVOH(MIN)とVOL(MAX)の仕様値がアンプ出力の負荷条件によって大きく変わることだ。負荷抵抗の値には、特に注意を払う必要がある。

実際の計装アンプの例を示そう。0.6μAのデュアルオペアンプIC「TS1002」を使用した計装アンプだ。2.5Vの電源電圧で動作し、利得は10である。TS1002のVOH(MIN)およびVOL(MAX)の仕様値は、負荷抵抗が100kΩの場合に2.498Vと0.001Vになる。出力ダイナミックレンジが最大化するとともに出力が飽和せずに済む基準電圧VREFは、式(1)から(2.498V+0.001V)÷2=1.249Vとなる。利得が10で、出力が飽和せずに済む最大差動入力電圧は、式(2)から(2.498V+0.001V)÷(2×10)、つまり125mVと求められる。

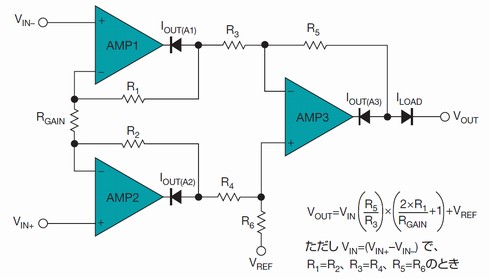

3個のオペアンプを使った計装アンプ回路

3個のオペアンプで構成した計装アンプの回路図を図5に示す。最大のダイナミックレンジを得るには、基準電圧VREFはAMP1およびAMP2の出力電圧振幅の中央に設定すればよい(式(1)を適用)。

回路利得の計算も図4と同じで、式(2)を使う。回路の出力電圧はVREFを基準に測定する。差動入力電圧の最大値は式(2)から求められる。

実際の例を示そう。Touchstone Semiconductorの4回路入りオペアンプIC「TS1004」を使って利得が50、電源電圧が2.5Vの計装アンプを設計した例である。TS1004のデータシートによると、VOH(MIN)およびVOL(MAX)の仕様値は100kΩ負荷に対し、それぞれ2.498V、0.001Vだ。式(1)から、出力段にはVREF=(2.498V+0.001V)÷2=1.249Vのオフセットを加えることで、出力ダイナミックレンジを最大化するとともに、出力段の飽和を避けられる。利得が50のときに、出力段が飽和せずに済む最大の差動入力電圧は、(2.498V+0.001V)÷(2×50)より25mWになる。

Copyright © ITmedia, Inc. All Rights Reserved.