IGBTやCMOS ICを使った回路に隠れた“落とし穴”:Wired, Weird(4/5 ページ)

配線が短いのでCMOS ICの入力処理は不要!?

落とし穴はCMOS ICの入力回路にある。

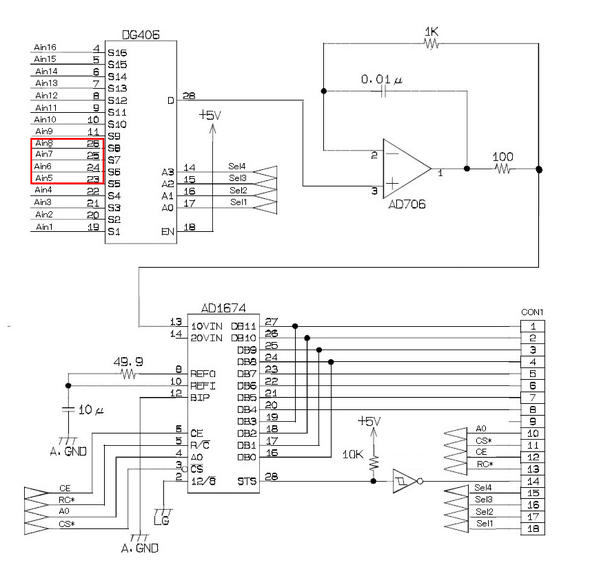

DG406のアドレス4ビット(A0からA3)とAD1674の制御入力(CE, RC, A0, CS)が直接コネクターに接続されて、この信号にはプルアップまたはプルダウンの処理がされていなかった。おそらくCPU基板との接続の配線が短いので基板の設計時にCMOS ICの入力処理は不要と判断して設計したと推定される。アナログ基板とCPU基板の距離が常に短い配線で接続されていれば、問題は小さいかもしれないが、現実的には問題が出やすい。

それは基板を作る時や検査する時は、基板は単体で扱われるからだ。つまり検査時に基板を接続する前までは2つの基板は分離されている。また基板の持ち運び時や接続時に作業者がコネクターを通してCMOS ICの入力端子に触れる可能性は非常に高い。

なお、基板工場では作業者は手にアース線を接続して組み立てと検査の作業を行っているので通常、基板に静電気がかかることはない。しかし、装置に基板を組み込むときや顧客の現場では、ごみの付着を防止するためナイロンの手袋をして作業しているため、基板に静電気が印加される可能性がある。

アナログ基板のノイズマージンが低下が原因

返却された基板を治具で確認したら動作不良だったが、オシロスコープのプローブを通してデバイスの入出力の波形を確認しながら検査すると不具合が再現しなくなった。このため、問題点はCPU基板とアナログ基板とのインタフェースに隠れていると考えられた。オシロスコープを外し、CMOS ICの入力端子に仮付けで47kΩの抵抗でプルダウンしても、治具で動作確認したら正常に動作した。その後、プルダウン抵抗を外して確認したがアナログ基板は正常に動作できるようになった。

アナログ基板のノイズマージンが低下したことが、不具合発生の原因であり、CMOS ICの入力処理を行っていないことがその遠因と考えられたので、プルダウン抵抗を追加する設計変更を客先へ申し入れた。

このようにCMOS ICの入力端子をコネクターに接続する場合には、必ず抵抗でプルアップまたはプルダウンの処理を行う必要がある。またこの処理を行うことで信号のインピーダンスが下がり、基板に実装された回路の耐ノイズ性も向上させることもできる。

Copyright © ITmedia, Inc. All Rights Reserved.