伝送路の特性とシグナルコンディショナーによるジッタの補償:高速シリアル伝送技術講座(11)(3/4 ページ)

送信端/受信端の半導体デバイスによる伝送路インサーションロスのISI補償

シグナルコンディショナーデバイスの送信端エンファシスドライバや受信端イコライザー(CTLE)の実装ではランダムジッタ(RJ)を低減することはできません。ですが、DJの1つである伝送路インサーションロス起因のISIジッタ(シンボル間干渉)を補償できます。 以下にその方法と動作について説明していきます。

出力ドライバによるインサーションロスの補償 〜 プリエンファシス/ディエンファシス

プリエンファシス/ディエンファシスドライバとも伝送路を通過した受信端での周波数依存の減衰を出力端で補う技術です。

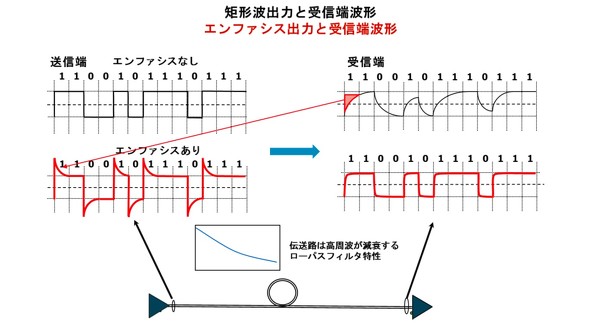

ケーブル、コネクター、基板などの伝送路のインサーションロスによって、受信端デバイスの入力信号は高周波が減衰し振幅が小さくなりますが、低周波は高周波と比較し減衰量は少ない状態です。この環境の逆特性になるようにあらかじめ送信端で高周波成分を低周波成分と比較して大きくし、受信端でのISIジッタを補償する方法がプリエンファシスとディエンファシスです。

図6右上の黒線の受信端波形は、伝送路のローパスフィルター特性により送信端矩形波の高周波が減衰し、エッジ部分のエネルギーが小さくなっています。

図6左下の赤線送信端のハイパスフィルターを通したような出力のエンファシス波形は、受信端で黒線の高周波が減衰したエッジ部分の波形を切り取って加えたような形になっており、受信端で減衰する高周波エネルギーを送信端で強調した出力とする事で、受信端のISIジッタを補償しています。

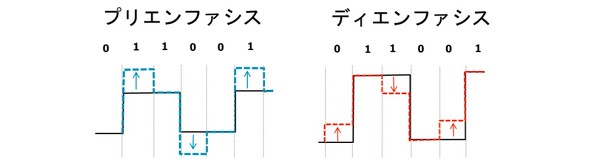

プリエンファシスとディエンファシスはどちらも相似形です。速度の低いアプリケーションではエッジレートが1UI(ユニットインターバル)と比較し十分余裕があり振幅を上げることが可能なため図7左のプリエンファシスを使用し、数〜数十ギガビット/秒(Gbps)の帯域ではエッジレートが高速な矩形波にさらにエッジレートを上げた高周波成分の追加は困難なため図7右の低周波部分を減衰させるディエンファシスの使用が一般的です。

またドライバのエンファシス量は振幅電圧もしくはピーク振幅と安定部分の振幅の差のデシベル(dB)で表示されます。

図6と図7のエンファシス波形を比較すると、図6の赤線出力波形では矩形波にハイパスフィルターを通したアナログ的なエンファシス波形で、ケーブルのローパスフィルター特性の逆特性により理想的に受信端のISIジッタを補正できています。しかし、シリアライザなどに実装される図7のようなデジタル処理とデータレートに依存したエンファシス波形では、本来必要な伝送路特性の逆特性の理想的なハイパスフィルター特性を作ることが難しく、エンファシス量を大きくしすぎると受信端のジッタを増やす原因にもなります。

Copyright © ITmedia, Inc. All Rights Reserved.

図6:エンファシスあり、なしのドライバ出力とその受信端波形

図6:エンファシスあり、なしのドライバ出力とその受信端波形 図7:左=プリエンファシス / 右=ディエンファシス

図7:左=プリエンファシス / 右=ディエンファシス