QSFP-DD光トランシーバーの給電方法:電源設計(2/3 ページ)

マルチフェーズアーキテクチャ

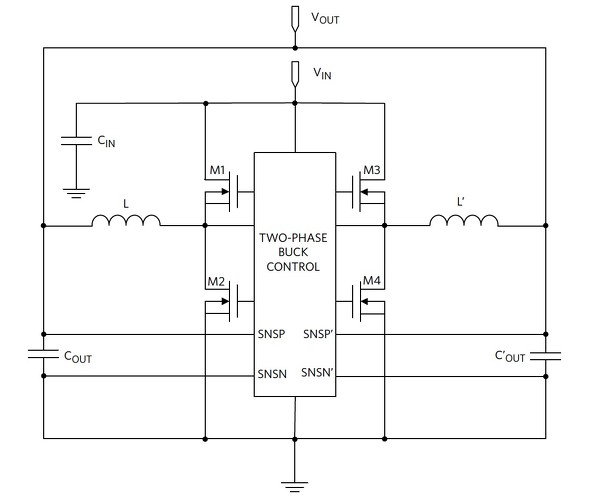

最大8Aのピーク電流を必要とするデジタルレールの場合、図5に示すような、2相インタリーブ方式、同期整流バックコンバーターアーキテクチャが最良のソリューションです。

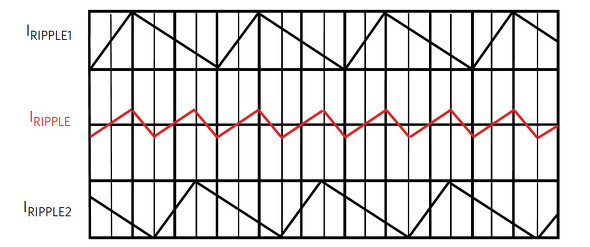

2つのインタリーブされた位相によって、リップル電流の低減とそれによるリップル電圧の低減が保証されます。低い総リップル電流が、比較的低い位相あたり動作周波数で実現されます。例として、図6は180度逆位相で33%デューティサイクルの2つのリップル電流の場合、2倍の周波数の単一位相に比べて総リップル電流が半分の大きさになることを示しています。より低い出力電流リップルおよび、電圧リップルがより高い周波数で得られるということは、出力に必要なコンデンサーが少なくて済むということであり、BOMの削減につながります。

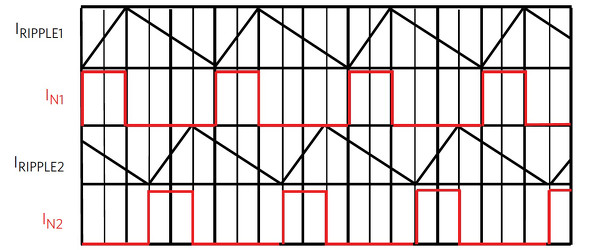

2相アーキテクチャは、必要な入力コンデンサーの数も少なくなります。総入力電流は、2つの逆位相電流(図7のIIN1および、IIN2)の和です。ここで、総入力電流が時間方向に分散されることで、入力電流の総RMS値が単相動作に比べて低減され、より小型の入力電流リップルフィルターの使用が可能になります。

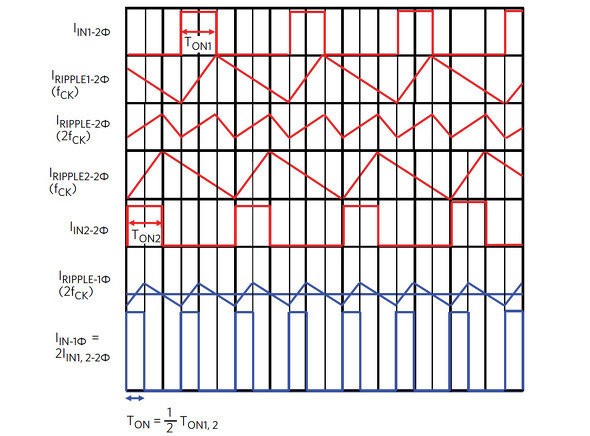

さらに、図8に示すように、2つの方式を同じ出力リップル周波数で動作させた場合、2相(2Φ、赤で表示)は単相(1Φ、青で表示)より効率的です。単相も、2相の2倍のスイッチング周波数(fSW)で動作することによって高周波数および低電流リップルを実現することができますが、スイッチング損失がより大きくなります。1つの周期内でのこの2つの方式の遷移は同数ですが、2相コンバーターの消費電流は単相コンバーターの(2倍の時間での)電流の半分であるため、スイッチング損失が低減します。

2相コンバーターのもう1つの大きい利点は、高速過渡応答および、負荷ステップ時の電圧オーバーシュート/アンダーシュートの低減です。位相あたりの電流が半分で、電流リップルが小さく、リップル周波数が2倍のため、スイッチング周波数を上昇させることが可能で、部品サイズをさらに低減し、温度制限に達することなくコンバーターのクローズドループ帯域幅を増大することができます。

最後に、総負荷電流が増大すると、受動部品のサイズも大きくなります。高負荷の場合、単相バックのインダクターは大型で非効率になります。多相動作では個々の相の電流が低減されるため、受動部品の最適なサイズが確保されます。

Copyright © ITmedia, Inc. All Rights Reserved.

図5:2相インタリーブ方式バックコンバーター

図5:2相インタリーブ方式バックコンバーター 図6:2相電流リップル低減と時間の関係

図6:2相電流リップル低減と時間の関係 図7:2相出力リップル電流および入力電流と時間の関係

図7:2相出力リップル電流および入力電流と時間の関係 図8:2相の電流と単相の電流と時間の関係

図8:2相の電流と単相の電流と時間の関係