フラッシュメモリにはウェイトステートがなぜ必要なのか:Q&Aで学ぶマイコン講座(45)(3/4 ページ)

実際の製品のウェイトステート

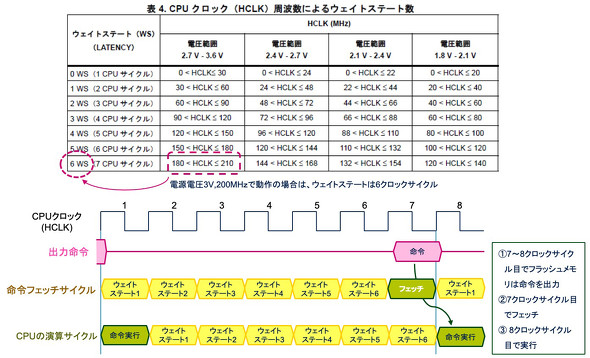

STマイクロエレクトロニクスのSTM32F75xシリーズのウェイトステート数の表を図4に示します。例えば電源電圧が3.0V、CPUクロック(システムクロック)を200MHzの動作条件で使いたい場合は、ウェイトステートは6クロックサイクルを挿入しなければなりません。

フラッシュメモリの命令読み出しが始まってから、7クロックサイクル目に確定した命令が出力されますので、その前に6クロックサイクル分のウェイトステートを挿入して、命令フェッチを待つことになります。7クロックサイクル目にフェッチされた命令は8クロックサイクルで実行されます。

STM32F75xシリーズは起動時、ウェイトステートの必要がない低い周波数のシステムクロックで動作します。その後ユーザーがシステムクロックを高速の周波数に変更しますが、最初にウェイトステートをシステムクロック周波数に適した値に設定し、その後周波数を上げます。これで、フラッシュメモリから命令を問題なく読み出すことができます。

ただし、これではせっかくシステムクロックを高速の200MHzに設定しても、フラッシュメモリの読み出し時間がネックになってCPUのパフォーマンスが生かされません。

そこで、実際の製品では、そのような問題が起きない回路が仕組まれています。次の章でその仕組みを説明します。

ウェイトステートのオーバーヘッドを防ぐ仕組み

ウェイトステートによるフラッシュメモリの読み出し時間のオーバーヘッドの対策は、各マイコンでさまざまな回路が施されていますが、ここではSTマイクロエレクトロニクスのSTM32ファミリで行われている対策を解説します。詳細は製品ごとで異なり、また社外秘の部分が多いため、対策内容のイメージをつかんでもらえる程度の大まかな説明にとどめます(図5参照)

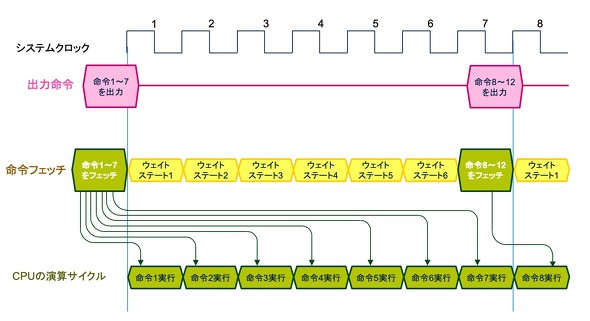

対策のポイントは、フラッシュメモリから命令を読み出す時に、1命令ではなくて複数命令を1度に読み出すことです。図4で示したウェイトステートが6クロックサイクル必要な場合であれば、1度に7命令読み出します。そして、7命令分を格納できるプリフェッチバッファを設き、そこに一時的に保管します。プリフェッチバッファは、レジスタなどのラッチ回路で構成しておいて、読み出し時間に遅延のない回路を使います。

CPUは、ウェイトステートの期間にプリフェッチバッファから命令を順次読み出して実行します。すなわち、ウェイトステート1の期間は命令1、ウェイトステート2の期間は命令2……というように実行します。すると、ちょうどプリフェッチバッファが空になる時に、次の7命令がフェッチされます。これを繰り返すことで、フラッシュメモリの読み出し時間のオーバーヘッドは解消します。

しかし、これでも分岐命令や割り込みの時に、プリフェッチバッファには入っていない命令を実行しなければならない場合は、フラッシュメモリの読み出し時間のオーバーヘッドが発生します。そのような場合はキャッシュ*3)などの補助メモリを使うことで、オーバーヘッドは解消されます。

Copyright © ITmedia, Inc. All Rights Reserved.