ΔΣADC内ノイズの概要 ―― 本当に必要なノイズ特性は何かを探ってみる:アナログ設計のきほん【ADCとノイズ】(3)(4/4 ページ)

より高いノイズ特性を持つADCでは?

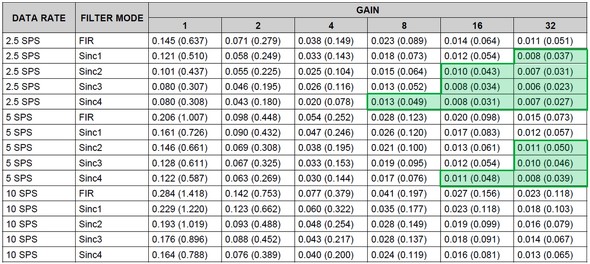

図6は32ビットADCである『ADS1262』のノイズ表です。このADCは機能的にADS124S08と似ていますが、より高いノイズ特性を持っています。緑で塗りつぶした部分は、50nVPP以下の入力換算ノイズが得られるデータレートとノイズの組み合わせを示しており、ADS1262がシステム変更後の分解能要件を満たすことを裏付けます。

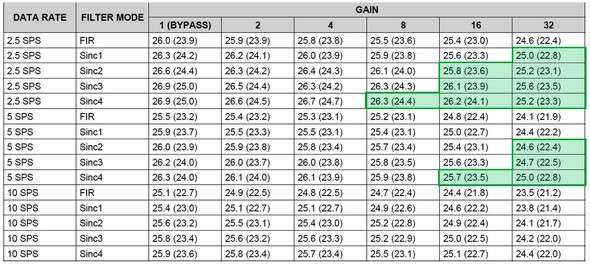

入力換算ノイズの結果を相対パラメーターと比べてみましょう。図7で強調表示した部分は、図6と同じデータレートとゲインの組み合わせでのADS1262のノイズフリー分解能性能です。

第2回で、多くのエンジニアが無駄にノイズフリー分解能(ダイナミックレンジ)を最大化しようと考えていると指摘しました。システムで必要な5SPSデータレートのときに、強調表示された最大値からシステムのノイズフリー分解能を計算して、このポイントを検討してみましょう。図7では、この値は23.5ビットであり、Sinc4フィルターを使用してゲインが16V/Vのときに得られます。

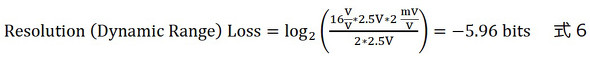

図7の表題に、システム仕様の2.5Vではなく5Vの基準電圧を表の計算に使用すると書かれていることを思い出してください。この差を埋めるには、図6の分解能の値それぞれを1ビットずつ減らさなければなりません。つまり、ある特定の条件で最大で22.5ビットのノイズフリー分解能しか期待できないということです。ここで、これらの設定のときのADS1262の予想分解能損失を計算できます。

式6の結果を使用すると、システムのノイズフリー分解能は32ビットADC使用時に16.5ビットしかありません。

多くの人にとって、これはがっかりするような結果です。実際には得られないADCの性能にお金を払っているのではないかという懸念が当たっているように思えます。しかし、図6で同じ設定を見ると、実際には特定の条件のときに48nVPPノイズをうまく活用していることに気付くでしょう。これは、16ビットADCはもちろん、ほとんどの24ビットADCでも得られない非常に小さい値です。

最終的に、これが私の主張したいポイントです。システムで超低ノイズ特性が必要とされるため、16.5ビットのノイズフリー分解能(ダイナミックレンジ)を達成するには、このような高分解能ADCが必要です。このようなことから、システム性能を定義し、ADCの選択に入力換算ノイズを使用することが理に適っているのです。

次回は、有効ノイズ帯域幅を詳しく説明し、システムに入るノイズの量を確認する方法やノイズ帯域幅を制限する方法などのトピックを掘り下げる予定です。

著者紹介

ブライアン・リゾン(Bryan Lizon)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア

関連記事

A-Dコンバーターの「ノイズ・スペクトル密度」を理解する

A-Dコンバーターの「ノイズ・スペクトル密度」を理解する

信号アクイジションシステムについては、数十年にわたってより広い帯域幅が求められる状況が続いています。その結果、高速A-Dコンバーター(ADC)で最も重視される性能項目にも緩やかな変化が生じています。それに伴い、ADCの性能は、従来とは異なる方法で測定されるようになってきました。 IoTにおける“精度”の重要性

IoTにおける“精度”の重要性

IoT(モノのインターネット)では、高精度にデータを計測、センシングする必要があります。高い精度での計測、センシングは、IoTにさまざまな利点をもたらすためです。ここでは、いかにIoTにおいて、計測/センシングの精度が重要であるかを事例を挙げつつ、考察していきます。 オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数

オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数

第2部では、2つの極の概要とそれらがフィルターの最終的な性能に対してもたらす歪みについて考察しながら、タイプ2の補償回路の伝達関数を決定する方法を説明します。 オペアンプのダイナミック応答の検討(1) タイプ2補償回路の使用時

オペアンプのダイナミック応答の検討(1) タイプ2補償回路の使用時

補償回路は、理想的な特性を想定したオペアンプを中心に構築したアクティブ回路が使用されます。ですが、理想的なオペアンプを想定した計算は成立せず、最終的にゲインと位相の深刻な歪みを招く結果になります。開ループゲインと、低周波および高周波にある2つの極が全体的な応答の形状をどのように規定するかが明らかになると、適切なオペアンプを選択できます。 高速、高電圧絶縁のための絶縁LVDSバッファ

高速、高電圧絶縁のための絶縁LVDSバッファ

絶縁と長い距離にわたる高速相互接続を両立する場合、絶縁LVDS(低電圧差動信号)バッファが有効です。そこで、絶縁LVDSバッファの活用例を紹介するとともに、昨今の絶縁要件などを考察し、最新の絶縁LVDSバッファソリューション例を紹介します。 DACの精度を改善するためのトリミング

DACの精度を改善するためのトリミング

高い精度が求められるシグナルチェーンに必須の部品である高精度D-Aコンバーター(DAC)。高精度DACはトリミング(校正)を行うことで、信号精度をさらに高めることができる。本稿では、DACに使われる2つのアーキテクチャ「R2Rラダー」と「ストリングDAC」について説明しながら、両アーキテクチャで精度向上に役立つトリミング手法を検討する。

Copyright © ITmedia, Inc. All Rights Reserved.