デルタ-シグマADC使用時における電源ノイズ影響の低減:アナログ設計のきほん【ADCとノイズ】(最終回)(4/4 ページ)

電源の問題を防ぎ、解決するには

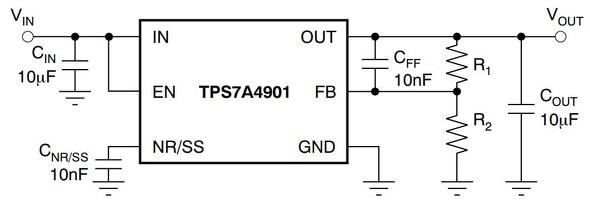

ADCの電源設計を見直す際には、潜在的な問題を除外して最初の段階を無事通過するために、いくつかのパラメーターを確認するところから始めるとよいでしょう。各部品の出力電流制限や入出力電圧範囲といった、主要な電源仕様を見直すことから始めましょう。電源を共有するすべてのアクティブ部品の総消費電流を考慮し、バジェットに余裕を組み込むようにしてください。また、電源の出力の最大容量性負荷を確認してください。その電源のバルクとローカルのすべてのデカップリングコンデンサーは実質的に並列であり、簡単に合計できます。容量が大きすぎると、起動が遅くなる可能性があります。最後に、LDOの入力と出力の間に少なくとも最小ドロップアウト電圧があることを確認してください。図13に示すように、フィルタリングを強化するために、推奨するその他のノイズ低減コンデンサー(CNR)やフィードフォワードコンデンサー(CFF)の追加も検討してください。

使用する電源が正しく設定されているのが確認できたら、フィルタリング強化のためにADCのデカップリングコンデンサーのサイズを大きくして、ノイズ特性全体の改善に取り組みましょう。これは、主電源ピンだけでなく、外付けデカップリング用の専用ピンにつながるどの内部電圧ノードでも有用です。それらに対しても普通はADCメーカーが推奨する容量値があります。最高の性能を得るには、容量の大きいコンデンサーと並列に容量の小さいコンデンサーを配置し、小さい方のコンデンサーがデバイスピンに近くなるように配置することを忘れないでください。

最後に、電源調整部品自体のせいでADCスペクトルにトーンが生じると考えられる場合は、それぞれのADC電源を一度に1つずつ、外部ベンチ電源と置き換えてみてください。これでも問題箇所が明らかにならない場合は、ノイズの発生源を特定するために、基板の主電源を置き換えてみるのもいいでしょう。

これで、連載「アナログ設計のきほん/ADCとノイズ編」を終わります。楽しみながらアナログシグナルチェーン設計のノイズについて理解を深めていただけたなら幸いです。

著者紹介

ブライアン・リゾン(Bryan Lizon)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア

関連記事

高分解能ΔΣADC回路のリファレンスノイズ低減

高分解能ΔΣADC回路のリファレンスノイズ低減

システム全体でリファレンスノイズのレベルに与えるゲインの影響を低減するための方法をいくつか分析し、リファレンスノイズについての説明をまとめていきます。低分解能ADCと高分解能ADCに対するリファレンスノイズの影響の違いも考察します。 デルタ−シグマADCでの電圧リファレンスノイズの影響

デルタ−シグマADCでの電圧リファレンスノイズの影響

さまざまなノイズ源が高精度デルタ−シグマADCに与える影響をより深く理解するために、電圧リファレンスノイズについて取り上げます。 信号の分解:デルタ-シグマADCでのアンプ・ノイズの影響

信号の分解:デルタ-シグマADCでのアンプ・ノイズの影響

今回と次回は、アンプのノイズがデルタ-シグマA/Dコンバーター(ADC)に与える影響について考察します。まずは、「出力換算ノイズと入力換算ノイズ」「ADCの入力にアンプを追加」「低分解能ADCと高分解能ADCの比較」について扱います。 高精度デルタ-シグマADCの 有効ノイズ帯域幅(ENBW)の理解【算出方法】

高精度デルタ-シグマADCの 有効ノイズ帯域幅(ENBW)の理解【算出方法】

今回は、「ENBWの算出方法」「システム変更がENBWに与える影響」について、2段フィルターを使用したシンプルな例を説明しながら、デルタ-シグマA/Dコンバーター(ADC)やシステムレベルの設計と絡めて考察していきます。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

図13:LDOのフィルタリングコンデンサー

図13:LDOのフィルタリングコンデンサー