セラミックキャパシター(6) ―― 新しい構造:中堅技術者に贈る電子部品“徹底”活用講座(50)(3/3 ページ)

貫通形3端子キャパシター

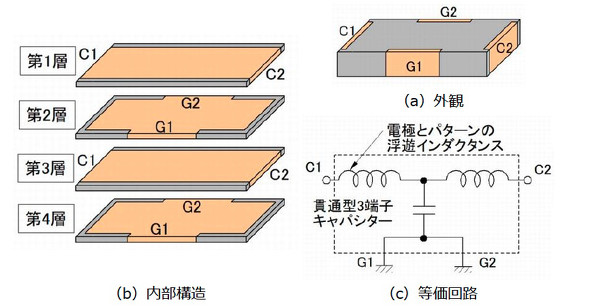

図5の貫通形キャパシターは筐体を利用したものでしたが実際の機器ではプリント基板上にもフィルターが必要になる場合があります。

図6に示す3端子貫通キャパシターはこの用途に使用されるものでパターンの浮遊(寄生)インダクタンスと静電容量とでフィルターを構成します。

配線パターンの途中にキャパシターのC1, C2端子を挿入するとノイズ電流は全て静電容量でバイパスされますので高いフィルター能力を得ることができます。また同様の考え方を円板形キャパシターに応用した製品もキャパシターメーカー各社から販売されています。

他にも分布定数を考慮した構造の「ブロードライザー」があります。これは分布定数形構造を持つ低ESL化導電性高分子キャパシターを用いた電源バイパス用キャパシターであり、100MHz以下で電源ラインの低インピーダンス化を目的としたものです。

3端子XYキャパシター

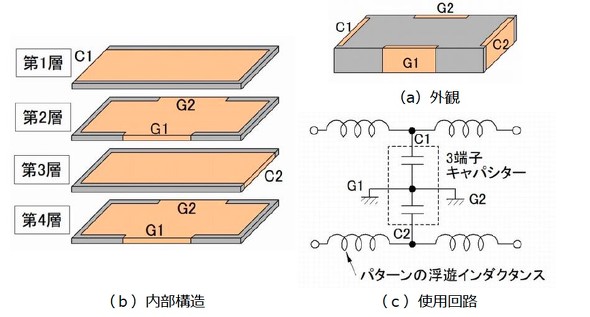

図5、図6の貫通キャパシターは基本的には信号線〜接地間の単ライン用として使用します。

しかし実際の機器では同相形の信号線もあり、単に同相入力それぞれにフィルターを設けるだけでは形状、価格面で十分な利点を得ることはできません。

3端子XYキャパシターはこのような箇所に使われるフィルター用のキャパシターでその外観と内部構造を図7(a)、(b)に示します。

内部構造や外観は貫通形キャパシターによく似ていますがキャパシター電極C1,C2間はDC的には接続されておらず、電極間にグランド層と呼ばれる電極を設け、さらにこのグランド層は低インピーダンス化を図るためにマルチ電極化(G1, G2)されています。

この3端子XYキャパシターを同相入力間に設けることで図4(c)に示すようにパターンの浮遊インダクタンスを利用して両ラインのノイズを同時にフィルタリングします。

今回はセラミックキャパシターの新しい構造について説明しましたが高周波になるとさまざまな因子が影響して汎用のセラミックキャパシターでは本来の性能が十分に発揮できません。やはり適材適所が重要かと思います。

次回は今回説明しなかったディレーティングや使用上の注意点について説明し、セラミックキャパシターについてまとめたいと思います。

【参考文献】

1)Wikipedia “Ceramic Capacitor”

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

セラミックキャパシター(5) ―― 高誘電率系キャパシターの温度特性

高誘電率系のキャパシターの温度特性について説明します。この種のキャパシターの温度特性は数式で変化の様子を表すことができません。したがって図表や文章での説明が主体になります。 セラミックキャパシター(4) ―― 温度特性

セラミックキャパシター(4) ―― 温度特性

セラミックキャパシターの温度特性について説明をしていきます。なお、今回、取り上げる温度特性はIEC規格クラス1やその日本版であるJIS規格のクラス1です。 セラミックキャパシター(1) ―― 原理、歴史などその概要

セラミックキャパシター(1) ―― 原理、歴史などその概要

今回からはキャパシターの一種であるセラミックキャパシターについて説明をしていきます。セラミックキャパシターは誘電体にセラミックス、つまり磁器や陶器に類する無機材料を使用したキャパシターを言い、このことがよくも悪くもセラミックキャパシターを特徴付けています。本稿では、小型のセラミックキャパシターについて説明をしていきます。 導電性高分子アルミ電解キャパシター(1)―― 導電性ポリマーとは

導電性高分子アルミ電解キャパシター(1)―― 導電性ポリマーとは

今回から「導電性高分子アルミ電解キャパシター」について取り上げます。今回は、導電性ポリマーとはどのようなものかなど、導電性高分子アルミ電解キャパシターの概要を説明します。 アルミ電解コンデンサー(1)―― 原理と構造

アルミ電解コンデンサー(1)―― 原理と構造

今回から、湿式のアルミ電解コンデンサーを取り上げます。古くから、広く使用される“アルミ電解コン”ですが、さまざまな誤解、ウワサ話があるようです。そこで、誤解やウワサに触れつつ、アルミ電解コンの原理や構造、種類などを説明していきます。 フィルムキャパシター ―― 特性と構造

フィルムキャパシター ―― 特性と構造

今回はWebでの情報を尊重してキャパシター自体の説明は必要最小限度にとどめ、使い方を主体的に考えていきます。最初はフィルムキャパシターを取り上げます。

Copyright © ITmedia, Inc. All Rights Reserved.

図6:3端子貫通キャパシター

図6:3端子貫通キャパシター 図7:3端子XYキャパシター

図7:3端子XYキャパシター