計装アンプ

計装アンプ

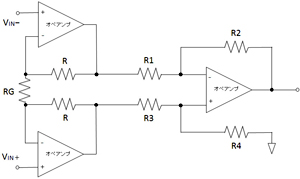

計装アンプ(インスツルメンテーション・アンプ)とは、オペアンプや抵抗器を組み合わせて構成した利得(ゲイン)ブロックのこと。オペアンプを3個使った回路構成が一般的だが、2個だけ使った回路構成などもある(図1)。

なぜ「計装」という名が付いているのか。その理由は、生産設備や製造装置における温度や圧力などの測定にアンプ回路を最適化した点にある。つまり、センサが検出した小振幅の微弱信号を、発生する雑音を低く抑えながら増幅する用途に最適化しているわけだ。ただし、それ以外の用途にも適用できる。例えば、モーター制御やデータ収集装置、車載機器などが代表的な用途である。

柔軟性は乏しいが、精度が高い

計装アンプの回路的な特徴について説明しよう。アナログ信号入力は差動形式であり、アナログ信号出力はシングルエンド形式である。差動信号入力を構成する2つの入力端子は平衡状態が確保されており、入力インピーダンスは数百MΩを超える。一方、出力インピーダンスは極めて低い値に設定されており、通常数mΩである。入力バイアス電流は、高い精度を実現するため、低い値に抑える必要がある。一般的には、nAオーダーであることが多い。

一般的なオペアンプと計装アンプとの回路的な違いは、柔軟性にある。オペアンプは、抵抗やコンデンサの接続方法を工夫することで、ユーザーの希望する利得に設定することができる。しかも、利得を設定できる範囲が広い。しかし、計装アンプでは、こうした柔軟な運用方法はできない。決められた比較的狭い設定範囲の中で利得を選択できるだけである。利得の設定には通常、抵抗を使う。このほか、端子(ピン)設定で利得を決めることができる品種もある。

現在、計装アンプICは、さまざまな半導体メーカーから製品化されている。例えば、米National Semiconductor社は、入力オフセット電圧が最大10μVで、その温度ドリフトが50nV/℃と非常に小さい計装アンプIC「LMP8358」を製品化している。温度ドリフトが非常に小さいため、一般に「ゼロ・ドリフト」と呼ばれる品種だ。入力バイアス電流も最大1.2nAと小さい。利得はシリアル・インタフェース(SPI)を介して、10、20、50、100、200、500、1000の中から1つの値を選択して設定できるほか、この利得範囲の中で2本の抵抗を使って任意の値に設定することも可能である。

テキサス・インスツルメンツのインタフェース製品ラインアップ

これだけは知っておきたいアナログ用語 バックナンバー

- DC-DCコンバータ

- スイッチング周波数

- POLコンバータ

- 同期整流

- LED駆動における直列接続と並列接続

- LED駆動と位相調光

- PWMとPFM

- 電源トポロジー

- EMI

- 特性インピーダンス

- SSCG

- コモン・モード雑音

- パワーMOSFET

- リニア・レギュレータ

- 電源シーケンス

- インダクタ

- コンデンサ

- 電源回路の制御モード:電圧モード制御、電流モード制御、リップル制御

- 熱抵抗

- オペアンプ

- A-Dコンバータ

- 計装アンプ

- パッシブ・フィルタ

- アクティブ・フィルタ

- ジッタ

- 8B10B

- 挿入損失(インサーション・ロス)と反射損失(リターン・ロス)

- AC結合とDC結合

- SDIとは

- プログレッシブとインターレース

- 差動プローブ

- プリエンファシスとデエンファシス

- イコライザ

- ヒステリシス制御方式

- コンスタント・オンタイム制御方式

- ECM

- ホットスワップ

- AWG

- クロック・データ・リカバリ

- LVDS

- アイ・ダイアグラム

- USB3.0

- フライバック方式

- 力率改善回路(PFC)

- MEMS

- KGD

- D-Aコンバータ

- 中間周波数

- SEPIC(セピック)

- スイッチング・レギュレータ

- ハプティクス(触感フィードバック)

- 圧電素子(ピエゾ素子)

- PSRR(電源電圧変動除去比)

- 負荷過渡応答

- FOD(異物検出機能)

- WPC(ワイヤレスパワーコンソーシアム)

- JESD204B

- SNRとSFDR

- 電池残量計IC

- Liイオン2次電池

- トライアック

- 定電流電源

- センサ

- アナログ・フロント・エンド(AFE)

- 高精度アンプ

- シグナル・チェーン

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本テキサス・インスツルメンツ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年3月31日

設計に役立つヒント集

宮崎 仁のQ&Aでよく分かるマイコン基礎の基礎:

第24回 割り込みっていろいろあるのですか?どんな種類があるか教えてください。

今回は、外部割り込み、内部割り込み、ソフトウェア割り込みについて詳しく解説しています

●全文を読む

電源IC選択のヒント集

電源IC 使用時の注意点をわかりやすく説明しているほか、使用時に発生する可能性のあるさまざまなトラブルとその対処法についても紹介しています。ぜひご利用ください。ダウンロードには myTI アカウントが必要です。

●Part 1をダウンロード

●Part 2をダウンロード

アナログ回路設計式一覧ポケット・ガイド

日本語版 PDF

英語版で高い評価を受けてきたポケット・ガイドの日本語版が完成しました。基板レベルやシステム・レベルの回路設計でよく使われるアナログ設計式を紹介しています。ダウンロードには myTI アカウントが必要です。

●ダウンロード